# 9602/DM9602 Dual Retriggerable, Resettable One Shots

#### **General Description**

These dual resettable, retriggerable one shots have two inputs per function; one which is active high, and one which is active low. This allows the designer to employ either leading-edge or trailing-edge triggering, which is independent of input transition times. When input conditions for triggering are met, a new cycle starts and the external capacitor is allowed to rapidly discharge and then charge again. The retriggerable feature permits output pulse widths to be extended. In fact a continuous true output can be maintained by having an input cycle time which is shorter than the output cycle time. The output pulse may then be terminated at any time by applying a low logic level to the RESET pin. Retriggering may be inhibited by either connecting the Q output to an active high input, or the  $\overline{\rm Q}$  output to an active low input.

#### **Features**

- 70 ns to  $\infty$  output width range

- Resettable and retriggerable—0% to 100% duty cycle

- TTL input gating—leading or trailing edge triggering

- Complementary TTL outputs

- Optional retrigger lock-out capability

- $\blacksquare$  Pulse width compensated for  $V_{CC}$  and temperature variations

- Alternate Military/Aerospace device (54xxx) is available. Contact a National Semiconductor Sales Office/Distributor for specifications.

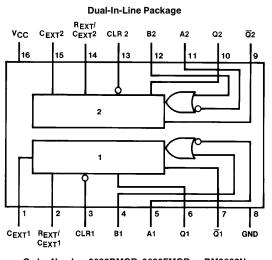

## **Connection Diagram**

#### **Function Table**

|                        | Operation |     |           |  |  |  |  |  |

|------------------------|-----------|-----|-----------|--|--|--|--|--|

| Α                      | В         | CLR | operation |  |  |  |  |  |

| H→L                    | L         | н   | Trigger   |  |  |  |  |  |

| н                      | L→H       | н   | Trigger   |  |  |  |  |  |

| Х                      | x         | L   | Reset     |  |  |  |  |  |

| H = High Voltage Level |           |     |           |  |  |  |  |  |

| L = Low Voltage Level  |           |     |           |  |  |  |  |  |

| X = Don't Ca           | re        |     |           |  |  |  |  |  |

©1995 National Semiconductor Corporation TL/F/6611

RRD-B30M105/Printed in U. S. A.

TL/F/6611-1

9602/DM9602 Dual Retriggerable, Resettable One Shots

June 1989

#### Absolute Maximum Ratings (Note)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage                       | 7V                             |

|--------------------------------------|--------------------------------|

| Input Voltage                        | 5.5V                           |

| Operating Free Air Temperature Range |                                |

| Military                             | -55°C to +125°C                |

| Commercial                           | $0^{\circ}C$ to $+70^{\circ}C$ |

| Storage Temperature Range            | -65°C to +150°C                |

Note: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the "Electrical Characteristics" table are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

## **Recommended Operating Conditions**

| Symbol          | Parameter<br>Supply Voltage    |                        | Military |      |      | Commercial |      |      | Units |

|-----------------|--------------------------------|------------------------|----------|------|------|------------|------|------|-------|

| oymbol          |                                |                        | Min      | Nom  | Max  | Min        | Nom  | Max  | Ginta |

| V <sub>CC</sub> |                                |                        | 4.5      | 5    | 5.5  | 4.75       | 5    | 5.25 | V     |

| VIH             | High Level Input               | $T_A = -55^{\circ}C$   | 2        |      |      |            |      |      | v     |

|                 | Voltage                        | $T_A = 0^{\circ}C$     |          |      |      | 1.9        |      |      |       |

|                 |                                | T <sub>A</sub> = 25°C  | 1.7      |      |      | 1.8        |      |      |       |

|                 |                                | T <sub>A</sub> = 75°C  |          |      |      | 1.65       |      |      |       |

|                 |                                | T <sub>A</sub> = 125°C | 1.5      |      |      |            |      |      |       |

| V <sub>IL</sub> | Low Level Input                | $T_A = -55^{\circ}C$   |          |      | 0.85 |            |      |      |       |

|                 | Voltage                        | T <sub>A</sub> = 0°C   |          |      |      |            |      | 0.85 | 1     |

|                 |                                | $T_A = 25^{\circ}C$    |          |      | 0.9  |            |      | 0.85 | v     |

|                 | T <sub>A</sub> = 75°C          |                        |          |      |      |            | 0.85 | 1    |       |

|                 | $T_A = 125^{\circ}C$           |                        |          | 0.85 |      |            |      |      |       |

| I <sub>OH</sub> | High Level Output Current      |                        |          |      | -0.8 |            |      | -0.8 | mA    |

| IOL             | Low Level Output Current       |                        |          |      | 16   |            |      | 16   | mA    |

| T <sub>A</sub>  | Free Air Operating Temperature |                        | -55      |      | 125  | 0          |      | 75   | °C    |

## Electrical Characteristics over recommended operating free air temperature range (unless otherwise noted)

| Symbol          | Parameter                                  | Conditions (N                                                            | Min                 | Typ<br>(Note 1) | Max | Units |      |  |

|-----------------|--------------------------------------------|--------------------------------------------------------------------------|---------------------|-----------------|-----|-------|------|--|

| VI              | Input Clamp Voltage                        | $V_{CC} = Min, I_I = -12 \text{ mA}$                                     |                     |                 |     | -1.5  | V    |  |

| V <sub>OH</sub> | High Level Output<br>Voltage               | $V_{CC} = Min, I_{OH} = Max$<br>$V_{IL} = Max, V_{IH} = Min$<br>(Note 4) |                     | 2.4             |     |       | V    |  |

| V <sub>OL</sub> | Low Level Output                           | $V_{CC} = Min, I_{OL} = Max$                                             | MIL                 |                 |     | 0.4   |      |  |

|                 | Voltage                                    | V <sub>IL</sub> = Max, V <sub>IH</sub> = Min<br>(Note 4)                 | СОМ                 |                 |     | 0.45  | V    |  |

| I <sub>IH</sub> | High Level Input Current                   | $V_{CC} = Max, V_I = 4.5V$                                               |                     |                 |     | 60    | μΑ   |  |

| IIL             | I <sub>IL</sub> Low Level Input<br>Current | V <sub>CC</sub> = Max                                                    | $MIL V_I = 0.40V$   |                 |     | -1.6  |      |  |

|                 |                                            |                                                                          | $COM V_{I} = 0.45V$ |                 |     | -1.6  | mA   |  |

|                 |                                            | V <sub>CC</sub> = Min                                                    | $MIL V_I = 0.40V$   |                 |     | -1.24 |      |  |

|                 |                                            |                                                                          | $COM V_{I} = 0.45V$ |                 |     | -1.41 |      |  |

| los             | Short Circuit                              | $V_{CC} = Max, V_{OUT} = 1V$                                             | MIL                 |                 |     | -25   |      |  |

| Output Current  | (Notes 2 and 4)                            | СОМ                                                                      |                     |                 | -35 | - mA  |      |  |

| ICC             | Supply Current                             | V <sub>CC</sub> = Max                                                    | MIL                 |                 | 39  | 45    | m (  |  |

|                 |                                            |                                                                          | COM                 |                 | 39  | 50    | - mA |  |

Note 1: All typicals are at V\_{CC}\,=\,5V,\,T\_{A}\,=\,25^{\circ}C.

Note 2: Not more than one output should be shorted at a time.

Note 3: Unless otherwise noted,  $\mathsf{R}_{\chi}\,=\,$  10k for all tests.

Note 4: Ground PIN 1(15) for V<sub>OL</sub> on PIN 7(9) or V<sub>OH</sub> and I<sub>OS</sub> on PIN 6(10) and apply momentary ground to PIN 4(12). Open PIN 1(15) for V<sub>OL</sub> on PIN 6(10) or V<sub>OH</sub> and I<sub>OS</sub> on PIN 7(9).

| Symbol                            | Parameter                                           |                                                | Conditions                                                                   | Military |      | Commercial |      | Units |

|-----------------------------------|-----------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------|----------|------|------------|------|-------|

|                                   |                                                     |                                                |                                                                              | Min      | Max  | Min        | Max  |       |

| t <sub>PLH</sub>                  | Propagation Delay Time,<br>Low-to-High Level Output | Negative Trigger Input to True Output          | $C_L = 15 \text{ pF}$ $C_X = 0$ $R_X = 5 \text{ k}\Omega$                    |          | 35   |            | 40   | ns    |

| t <sub>PHL</sub>                  | Propagation Delay Time,<br>High-to-Low Level Output | Negative Trigger Input<br>To Complement Output |                                                                              |          | 43   |            | 48   | ns    |

| t <sub>PW</sub> (MIN)             | Minimum True Output<br>Pulse Width                  |                                                |                                                                              |          | 90   |            | 100  | ns    |

| Minimum Complement<br>Pulse Width |                                                     |                                                |                                                                              |          | 100  |            | 110  |       |

| t <sub>PW</sub>                   | Pulse Width                                         |                                                | $\begin{array}{l} R_{X} = \ 10 \ k\Omega \\ C_{X} = \ 1000 \ pF \end{array}$ | 3.08     | 3.76 | 3.08       | 3.76 | μs    |

| C <sub>STRAY</sub>                | Maximum Allowable Wiring<br>Capacitance             |                                                | Pins 2, 14 to<br>GND                                                         |          | 50   |            | 50   | pF    |

| R <sub>X</sub>                    | External Timing Resistor                            |                                                |                                                                              | 5        | 25   | 5          | 50   | kΩ    |

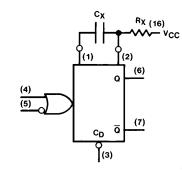

### **Logic Diagrams**

TL/F/6611-2

## **Operating Rules**

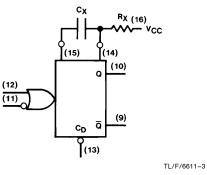

- 1. An external resistor (R\_{\chi}) and external capacitor (C\_{\chi}) are required as shown in the Logic Diagram.

- 2. The value of C<sub>X</sub> may vary from 0 to any necessary value available. If, however, the capacitor has leakages approaching 3.0  $\mu$ A or if stray capacitance from either terminal to ground is more than 50 pF, the timing equations may not represent the pulse width obtained.

- 3. The output pulse with (t) is defined as follows:

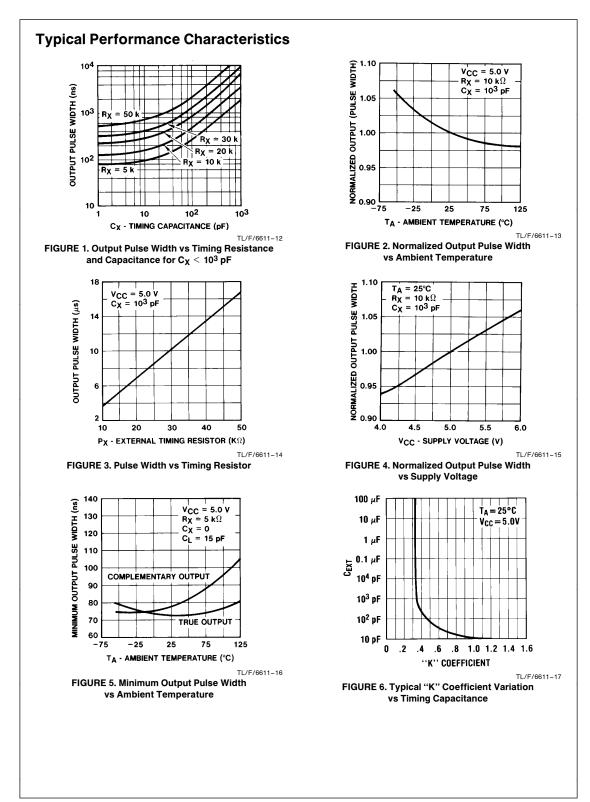

$$t = K R_X C_X \left[ 1 + \frac{1}{R_X} \right] \quad \begin{cases} \text{for } C_X > 10^3 \text{ pF} \\ K \approx 0.34 \end{cases}$$

where:

$$R_{\chi}$$

is in k $\Omega$ ,  $C_{\chi}$  is in pF

t is in ns

for  $C_X < 10^3$  pF, see *Figure 1.* for K vs  $C_X$  see *Figure 6.*

- 4. If electrolytic type capacitors are to be used, the following three configurations are recommended:

- A. Use with low leakage capacitors:

- The normal RC configuration can be used predictably only if the forward capacitor leakage at 5.0V is less than 3  $\mu$ A, and the inverse capacitor leakage at 1.0V is less than 5  $\mu$ A over the operational temperature range.

R

#### **Operating Rules** (Continued)

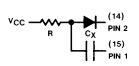

B. Use with high inverse leakage current electrolytic capacitors:

The diode in this configuration prevents high inverse leakage currents through the capacitor by preventing an inverse voltage across the capacitor. The use of this configuration is not recommended with retriggerable operation.

$t \approx 0.3 RC_X$

TL/F/6611-5

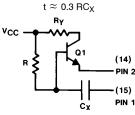

This configuration can be used to obtain extended pulse widths, because of the larger timing resistor allowed by beta multiplication. Electrolytics with high inverse leakage currents can be used.

${\sf R} < {\sf R}_X$  (0.7) (h\_FE Q1) or < 2.5  $M\Omega,$  whichever is the lesser

$R_X$  (min)  $< R_Y < R_X$  (max)

(5 k $\Omega \leq R_Y \leq$  10 k $\Omega$  is recommended)

C. Use to obtain extended pulse widths:

Q1: NPN silicon transistor with  $h_{FE}$  requirements of above equations, such as 2N5961 or 2N5962.

TL/F/6611-6

This configuration is not recommended with retriggerable operation.

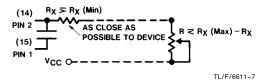

5. To obtain variable pulse width by remote trimming, the following circuit is recommended:

Under any operating condition, C<sub>X</sub> and R<sub>X</sub> (min) must be kept as close to the circuit as possible to minimize stray capacitance and reduce noise pickup. 7. Input Trigger Pulse Rules (See Triggering Truth Table) INPUT <sup>t</sup>рі н Q OUTPUT TL/F/6611-8 Input to Pin 5(11), (Pin 3(13) = HIGH) Pin 4(12) = LOW  $t_1$ ,  $t_3$  = Min. Positive Input Pulse Width > 40 ns t<sub>2</sub>, t<sub>4</sub> = Min. Negative Input Pulse Width > 40 ns 2.5 INPUT **t**PLH Q OUTPUT TL/F/6611-9 Input to Pin 4(12) (Pin 3(13) = HIGH)Pin 5(11) = HIGH8. The retriggerable pulse width is calculated as shown be $t_{W} = t + t_{PLH} = K R_X C_X \left(1 + \frac{1}{R_Y}\right) + t_{PLH}$ Q OUTPUT

TL/F/6611-10

- The retrigger pulse width is equal to the pulse width (t) plus a delay time. For pulse widths greater than 500 ns,  $t_W$  can be approximated as t. Retriggering will not occur if the retrigger pulse comes within  $\approx$  0.3  $C_X$  (ns) after the initial trigger pulse (i.e., during the discharge cycle).

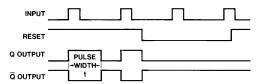

- 9. Reset Operation—An overriding clear (active LOW level) is provided on each one shot. By applying a LOW to the reset, any timing cycle can be terminated or any new cycle inhibited until the LOW reset input is removed. Trigger inputs will not produce spikes in the output when the reset is held LOW.

TL/F/6611-11

10.  $V_{CC}$  and Ground wiring should conform to good high frequency standards so that switching transients on  $V_{CC}$  and Ground leads do not cause interaction between one shots. Use of a 0.01 to 0.1  $\mu F$  bypass capacitor between  $V_{CC}$  and Ground located near the DM9602 is recommended.

\*For further detailed device characteristics and output performance, please refer to the NSC one-shot application note, AN-366.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications