### **Board Bringup: LCD and Display Interfaces**

Slides and Resources at http://www.elinux.org/BoardBringupLCD

Dave Anders aka prpplague

- Dave Anders aka prpplague

- Currently Contracted with TI

- Dave Anders aka prpplague

- Currently Contracted with TI

- Partners in TinCanTools

- Dave Anders aka prpplague

- Currently Contracted with TI

- Partners in TinCanTools

- Board Bring Up: LCD and Display Interfaces

- Dave Anders aka prpplague

- Currently Contracted with TI

- Partners in TinCanTools

- Board Bring Up: LCD and Display Interfaces

- Challenges of LCD Bring Up

- Dave Anders aka prpplague

- Currently Contracted with TI

- Partners in TinCanTools

- Board Bring Up: LCD and Display Interfaces

- Challenges of LCD Bring Up

- Interface Timings

- Dave Anders aka prpplague

- Currently Contracted with TI

- Partners in TinCanTools

- Board Bring Up: LCD and Display Interfaces

- Challenges of LCD Bring Up

- Interface Timings

- Display Interface Types

- Dave Anders aka prpplague

- Currently Contracted with TI

- Partners in TinCanTools

- Board Bring Up: LCD and Display Interfaces

- Challenges of LCD Bring Up

- Interface Timings

- Display Interface Types

- Debugging

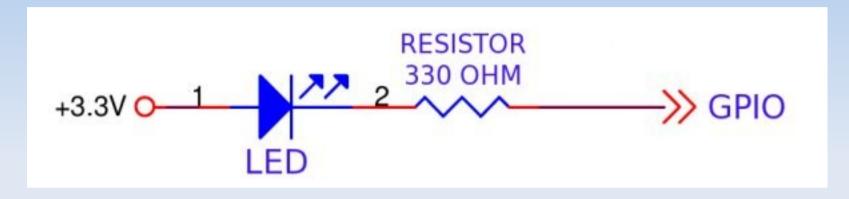

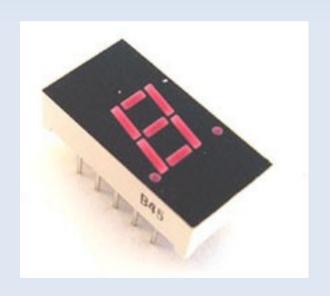

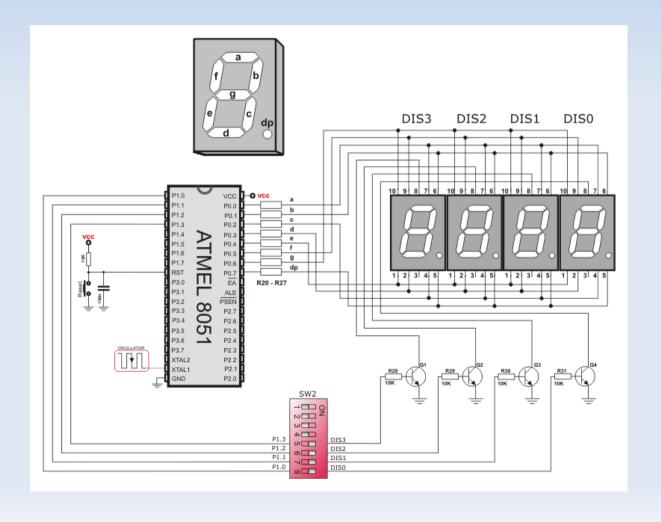

Simple User Display

Simple User Display

- Simple User Display

- Easy to visualize

- Easy to measure

- Easy to program

- Simple User Display

- Evolution of Displays

- Simple User Display

- Evolution of Displays

- Clocking

- Multiple signals

- Introduction of controllers

- Simple User Display

- Evolution of Displays

- Transition to LCD

- Simple User Display

- Evolution of Displays

- Transition to LCD

- Higher frequency

- More signals

- Complex Controllers

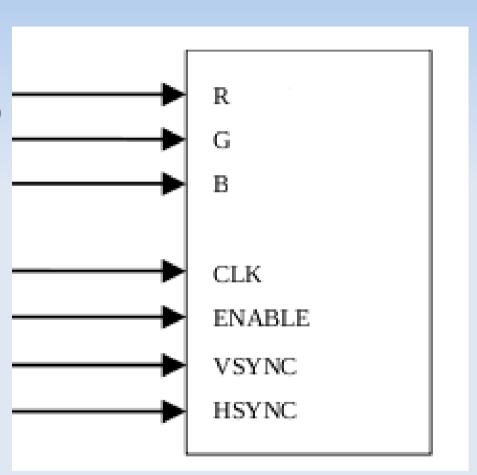

TFT Parallel Interface

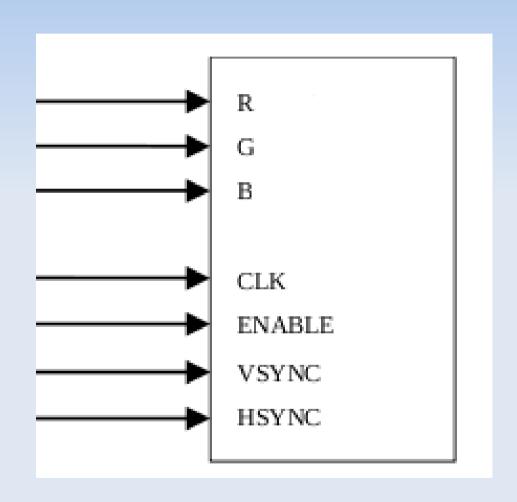

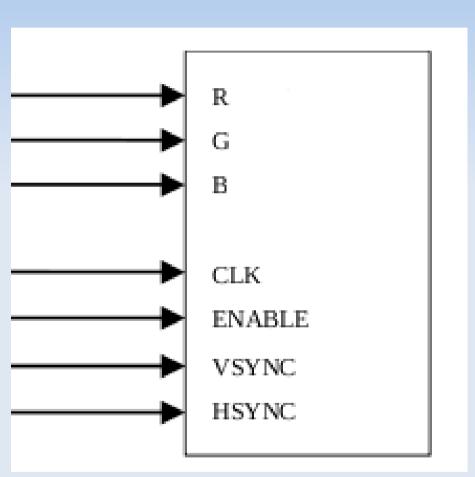

- TFT Parallel Interface

- PCLK (Pixel Clock)

- TFT Parallel Interface

- PCLK (Pixel Clock)

- HSYNC (Horizontal Sync)

- TFT Parallel Interface

- PCLK (Pixel Clock)

- HSYNC (Horizontal Sync)

- VSYNC (Verticle Sync)

- TFT Parallel Interface

- PCLK (Pixel Clock)

- HSYNC (Horizontal Sync)

- VSYNC (Verticle Sync)

- DE (Data Enable)

- TFT Parallel Interface

- PCLK (Pixel Clock)

- HSYNC (Horizontal Sync)

- VSYNC (Verticle Sync)

- DE (Data Enable)

- R/G/B (Data Lines)

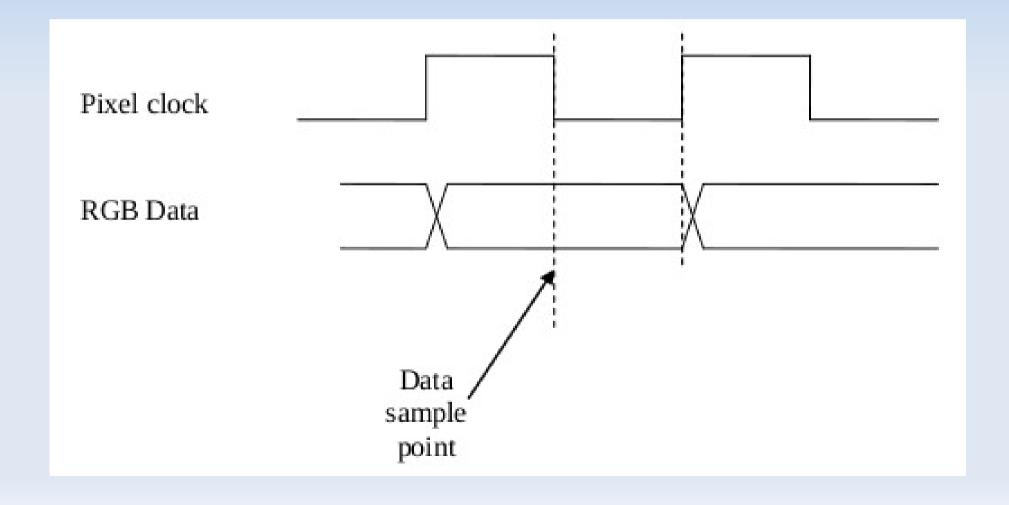

- TFT Parallel Interface

- Pixel Clock and RGB Data

- TFT Parallel Interface

- Pixel Clock and RGB Data

- 640 Width x 480 Height

- TFT Parallel Interface

- Pixel Clock and RGB Data

- 640 Width x 480 Height

- 640 x 480 = 307200 clocks for one frame

- TFT Parallel Interface

- Pixel Clock and RGB Data

- 640 Width x 480 Height

- 640 x 480 = 307200 clocks for one frame

- 307200 x 60 = 18432000 for 60 frames per second

- TFT Parallel Interface

- Pixel Clock and RGB Data

- 640 Width x 480 Height

- 640 x 480 = 307200 clocks for one frame

- 307200 x 60 = 18432000 for 60 frames per second

- Estimated PCLK = 18.432MHz

- TFT Parallel Interface

- Pixel Clock and RGB Data

- 640 Width x 480 Height

- 640 x 480 = 307200 clocks for one frame

- 307200 x 60 = 18432000 for 60 frames per second

- Estimated PCLK = 18.432MHz

- What if your SoC can not create exactly 18.432MHz?

- TFT Parallel Interface

- Pixel Clock and RGB Data

- 640 Width x 480 Height

- 640 x 480 = 307200 clocks for one frame

- 307200 x 60 = 18432000 for 60 frames per second

- Estimated PCLK = 18.432MHz

- What if your SoC can not create exactly 18.432MHz?

- Good question!!!!!

- TFT Parallel Interface

- Pixel Clock and RGB Data

- Line Timing HSYNC and DE

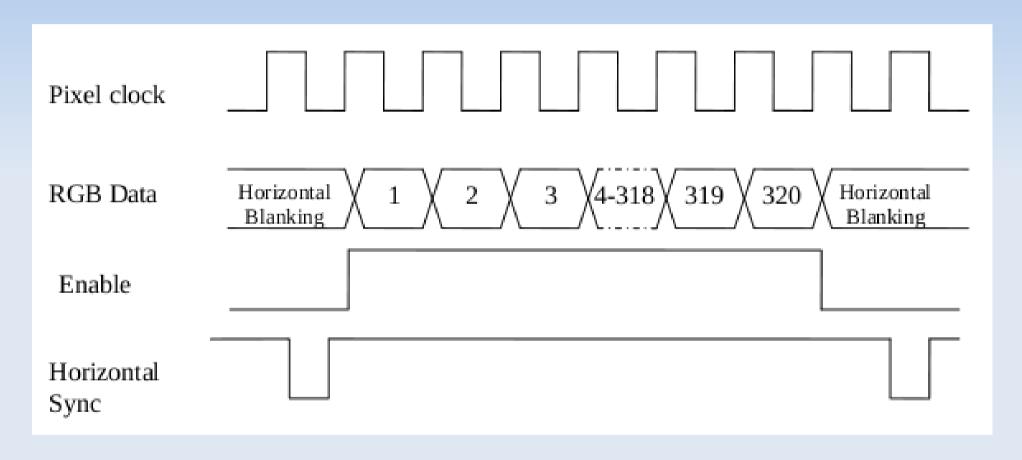

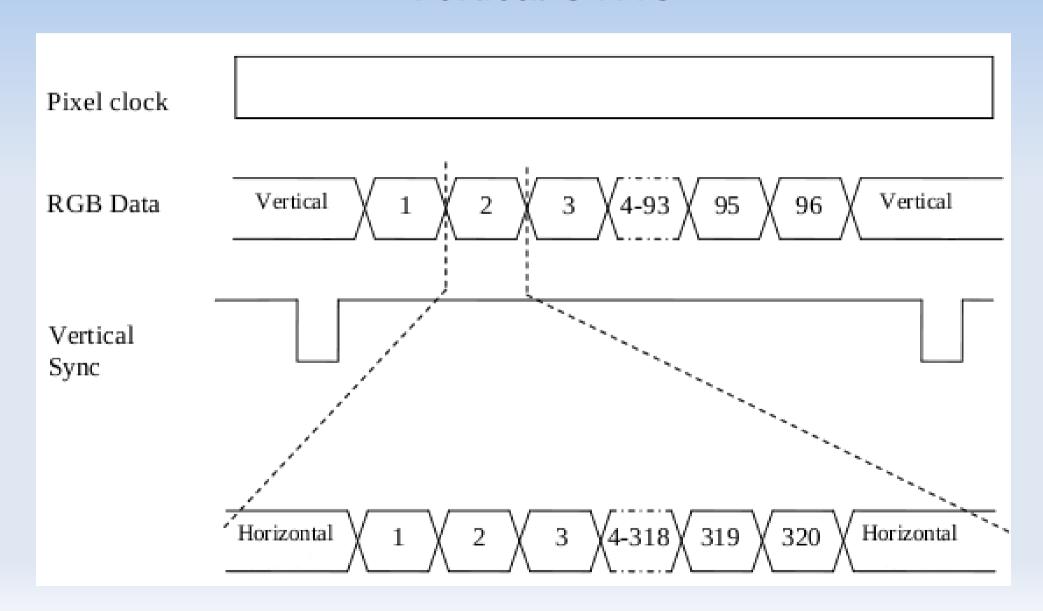

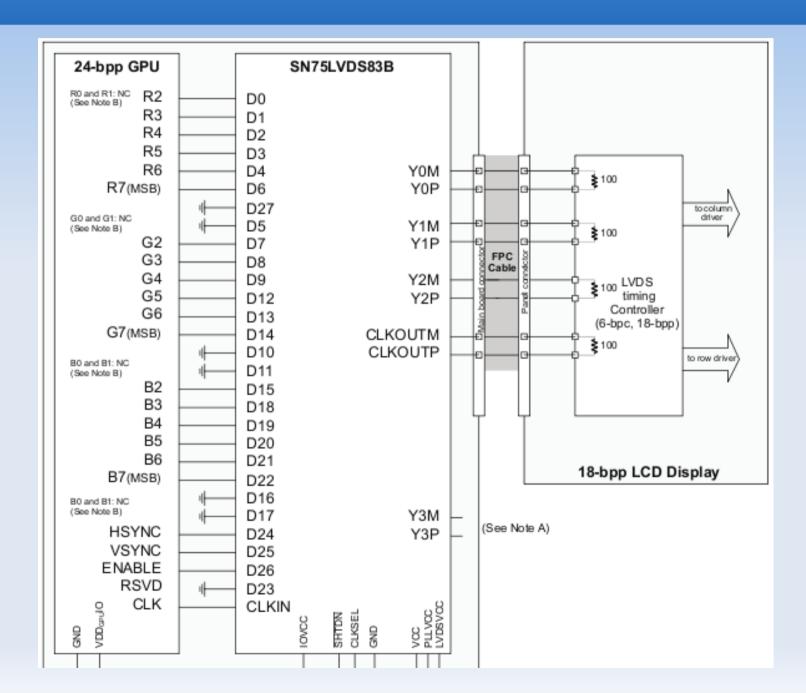

#### Horizontal SYNC and Data Enable

- TFT Parallel Interface

- Pixel Clock and RGB Data

- Line Timing HSYNC and DE

- Frame Timing VSYNC

#### **Vertical SYNC**

- TFT Parallel Interface

- Pixel Clock and RGB Data

- Line Timing HSYNC and DE

- Frame Timing VSYNC

- Front Porch / Back Porch / Sync Width

- Remember the question about exact pixel clock?

- TFT Parallel Interface

- Pixel Clock and RGB Data

- Line Timing HSYNC and DE

- Frame Timing VSYNC

- Front Porch / Back Porch / Sync Width

- Remember the question about exact pixel clock?

- Values in the datasheet

### **Interface Timings**

- TFT Parallel Interface

- Pixel Clock and RGB Data

- Line Timing HSYNC and DE

- Frame Timing VSYNC

- Front Porch / Back Porch / Sync Width

- Remember the question about exact pixel clock?

- Values in the datasheet

- Lots of numbers to keep track of

Disadvantages of Parallel Interface

- Disadvantages of Parallel Interface

- Large Number of Signals

- Limited Distance

- Lack of Standardization

- Disadvantages of Parallel Interface

- Differential Interfaces

- Disadvantages of Parallel Interface

- Differential Interfaces

- Reduced number of signals

- Longer distances

- Standardized

- Disadvantages of Parallel Interface

- Differential Interfaces

- Common Differential Interfaces

- Disadvantages of Parallel Interface

- Differential Interfaces

- Common Differential Interfaces

- LVDS Low Voltage Differential Signaling

- Disadvantages of Parallel Interface

- Differential Interfaces

- Common Differential Interfaces

- LVDS Low Voltage Differential Signaling

- DVI Digital Visual Interface

- Disadvantages of Parallel Interface

- Differential Interfaces

- Common Differential Interfaces

- LVDS Low Voltage Differential Signaling

- DVI Digital Visual Interface

- HDMI High-Definition Multimedia Interface

- Disadvantages of Parallel Interface

- Differential Interfaces

- Common Differential Interfaces

- LVDS Low Voltage Differential Signaling

- DVI Digital Visual Interface

- HDMI High-Definition Multimedia Interface

- DisplayPort

- Disadvantages of Parallel Interface

- Differential Interfaces

- Common Differential Interfaces

- Why learn TFT when working with Differential?

- Disadvantages of Parallel Interface

- Differential Interfaces

- Common Differential Interfaces

- Why learn TFT when working with Differential?

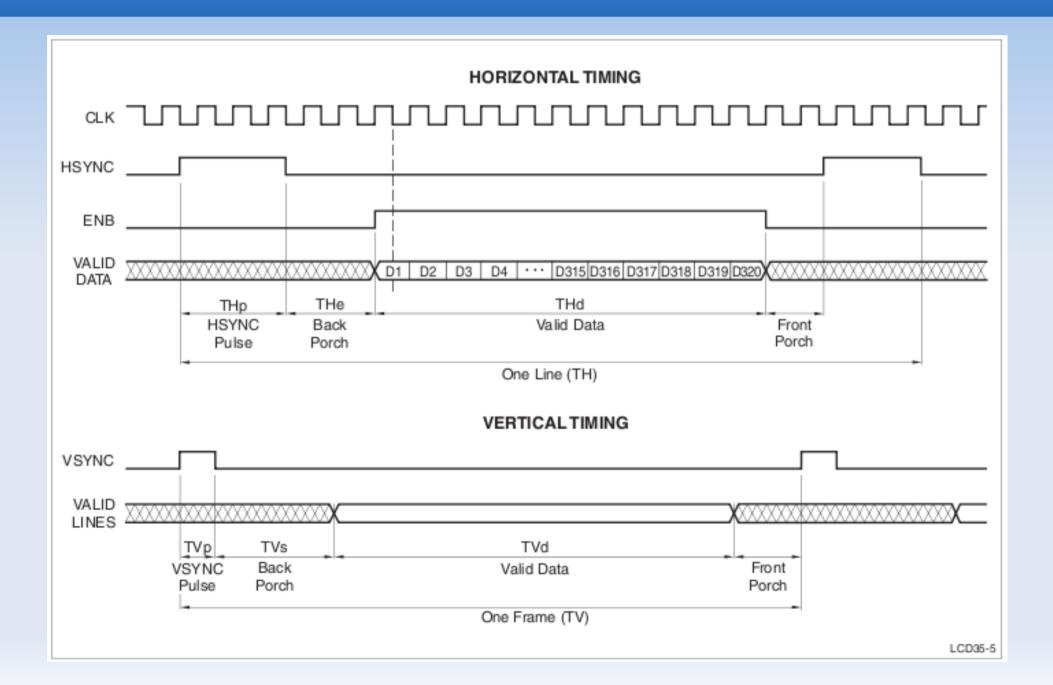

- LVDS SN75LVDS83B SN75LVDS82

- DVI TFP410 TFP401

- Disadvantages of Parallel Interface

- Differential Interfaces

- Common Differential Interfaces

- Why learn TFT when working with Differential?

- Combination Interfaces

- Disadvantages of Parallel Interface

- Differential Interfaces

- Common Differential Interfaces

- Why learn TFT when working with Differential?

- Combination Interfaces

- EDID

- Disadvantages of Parallel Interface

- Differential Interfaces

- Common Differential Interfaces

- Why learn TFT when working with Differential?

- Combination Interfaces

- EDID

- Extended Display Identification Data

- Disadvantages of Parallel Interface

- Differential Interfaces

- Common Differential Interfaces

- Why learn TFT when working with Differential?

- Combination Interfaces

- EDID

- Extended Display Identification Data

- Contents

- EDID Contents

- Multiple Configurations

- Pixel Clock Frequency

- Resolution

- Color Depth

- Front Porch / Back Porch

- SYNC width

- Disadvantages of Parallel Interface

- Differential Interfaces

- Common Differential Interfaces

- Why learn TFT when working with Differential?

- Combination Interfaces

- EDID

- Extended Display Identification Data

- Contents

- I2C EEPROM at 0x50

- Disadvantages of Parallel Interface

- Differential Interfaces

- Common Differential Interfaces

- Why learn TFT when working with Differential?

- Combination Interfaces

- EDID

- Extended Display Identification Data

- Contents

- I2C EEPROM at 0x50

- parse-edid

- Logic Analyzer

- Importance of visualization

- Logic Analyzer

- Importance of visualization

- Pixel clock frequency

- Logic Analyzer

- Importance of visualization

- Pixel clock frequency

- Open source (or open source friendly)

- Logic Analyzer

- Importance of visualization

- Pixel clock frequency

- Open source (or open source friendly)

- SIGROK

- ChronoVu LA8 (less than \$200)

- Logic Analyzer

- Reference Platform

- Same platform different display

- Different platform same display

- Compatible display

- Kernel sources

- Logic Analyzer

- Reference Platform

- Display Simulation

- Lower resolution

- Transmitter Chips TFP410 to DVI display

- Receive Chips LVDS to SN75LVDS82

- Logic Analyzer

- Reference Platform

- Display Simulation

- Userspace debugging

cat /dev/urandom > /dev/fb0

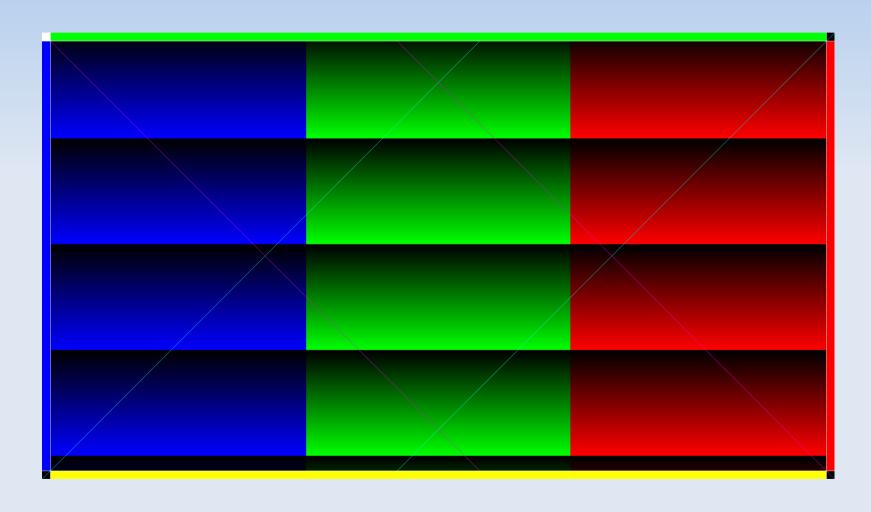

fb-test

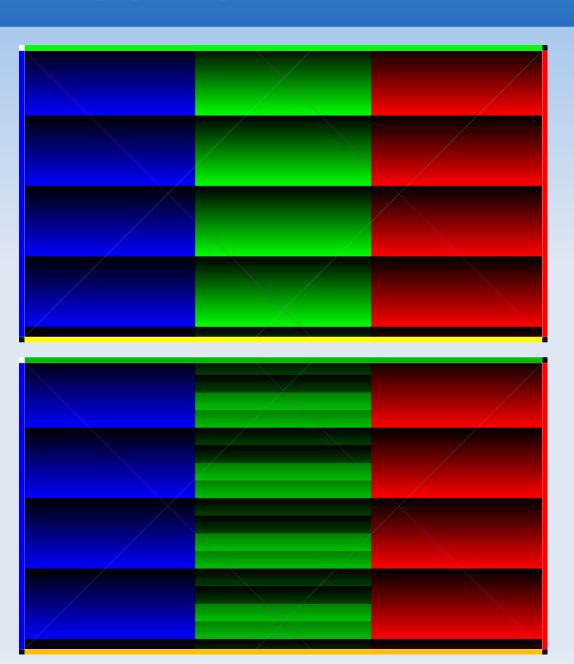

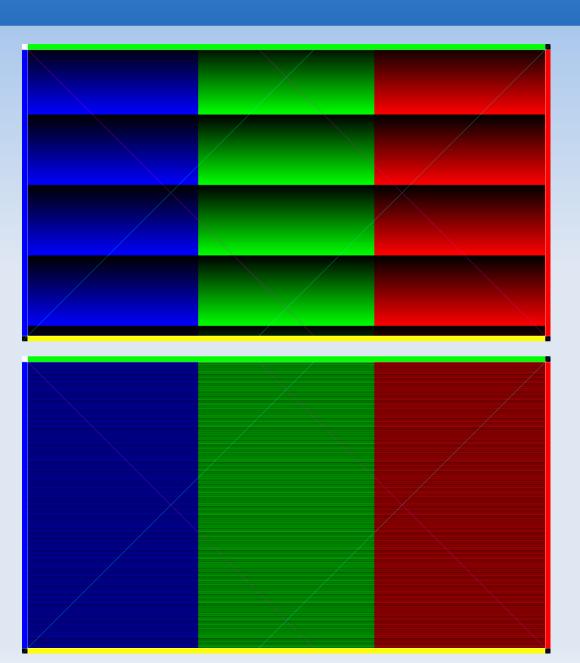

Missing Green

Data Bit

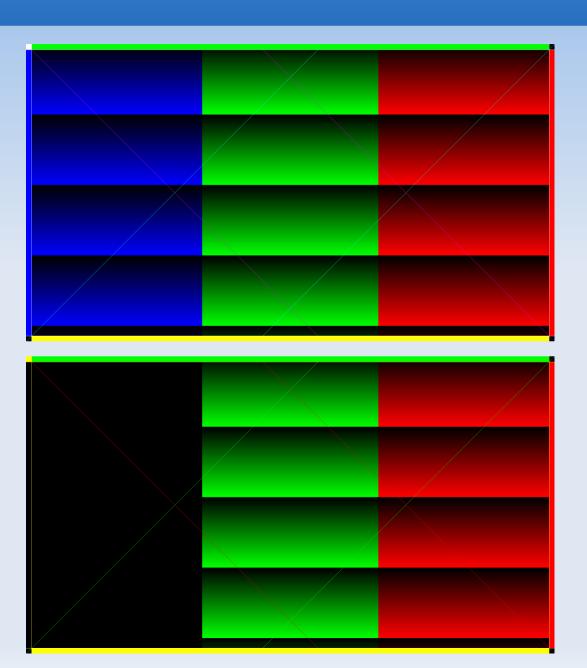

Missing Blue Signals

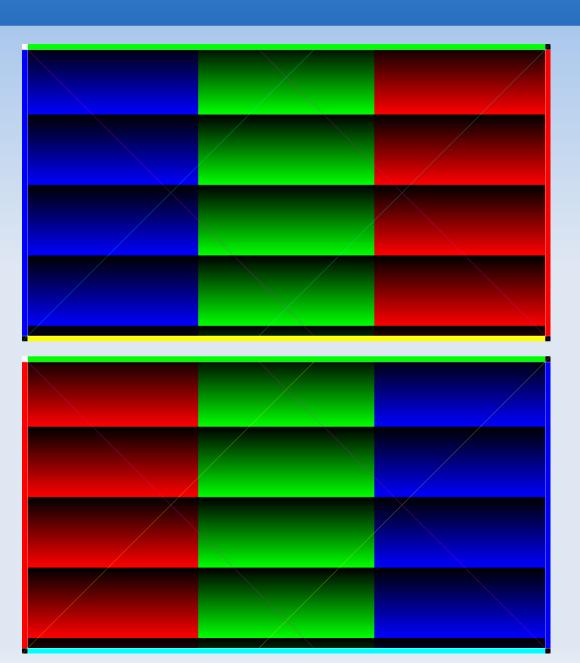

LSB/MSB Signal Swap

Red/Blue Signal Swap

#### Conclusion

- Summary

- Challenges of LCD bring up

- Interface Timings

- Display Interfaces

- Debugging

#### Conclusion

- Summary

- Challenges of LCD bring up

- Interface Timings

- Display Interfaces

- Debugging

- Resources

- http://www.elinux.org/BoardBringupLCD

#### Conclusion

Questions?