### **Editor's Column**

e appreciate all of your feedback on our first issue in September, 2006 on "The Technical Impact of

Moore's Law." With the Winter, 2007 issue, we are continuing our new policy of mailing a hard copy of the SSCS News to all 11,500 members. This issue is the first of four that SSCS plans to publish annually (one each in Winter, Spring, Summer, and Fall).

The goal of every issue is to be a self-contained resource on a select-

ed topic, with background articles (that is, the 'original sources') and new articles by experts who describe the current state of affairs in technology and the impact of the original papers and/or patents.

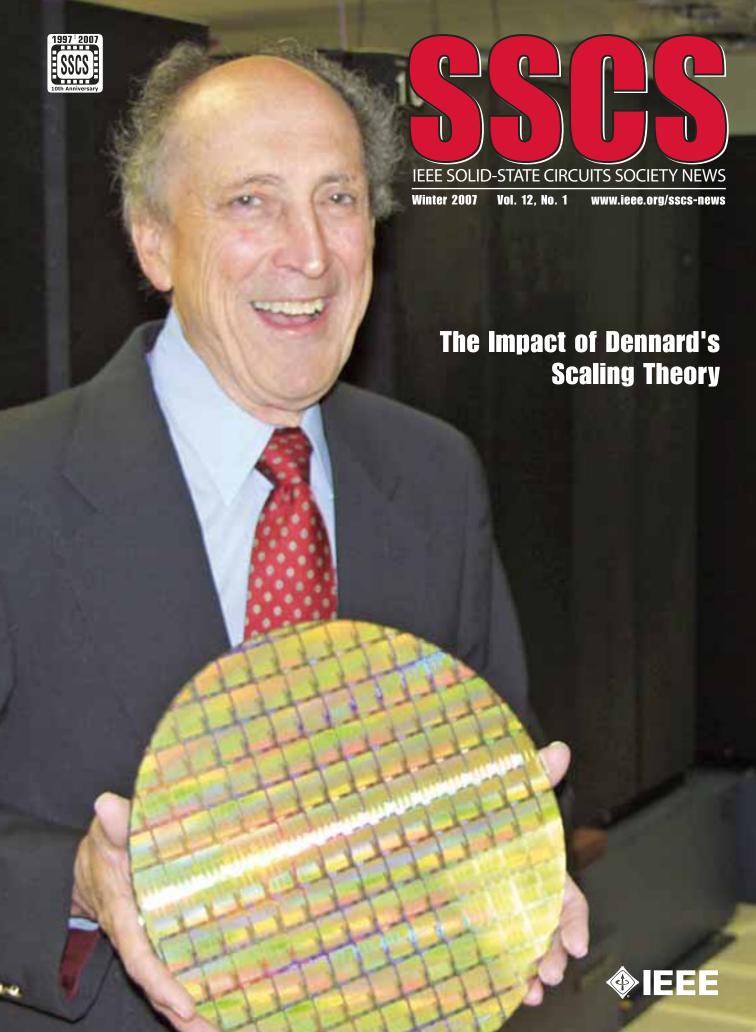

The theme of the Winter 2007 issue is "The Impact of Dennard's Scaling Theory."

This issue contains one Research Highlights article: "Analog IC Design at the University of Twente," by Bram Nauta, Head of the IC Design Group at the University of Twente, The Netherlands. The issue also contains seven short feature articles that address the theme:

- "A 30 Year Retrospective on Dennard's MOSFET Scaling Paper," by Mark Bohr of Intel Corporation;

- (2) "Device Scaling: The Treadmill that Fueled Three Decades of Semiconductor Industry Growth," by Pallab Chatterjee of i2 Technologies;

- (3) "Recollections on MOSFET Scaling," by Dale Critchlow, the University of Vermont;

- (4) "The Business of Scaling," by Rakesh Kumar, TCX, Inc. Technology Connexions;

- (5) "A Perspective on the Theory of MOSFET Scaling and its Impact," by Tak Ning, IBM;

- (6) "Impact of Scaling and the environment in which the Scaling developed

- at that time," by Yoshio Nishi, Stanford University;

- (7) "It's All About Scale," by Hans Stork, TI.

Three original papers by Dennard, from 1972 (IEDM Conference), 1973 (IEDM Conference), and 1974 (IEEE Journal of Solid-State Circuits), are also reprinted in this issue.

Thank you for taking the time to read the SSCS News. We appreciate your comments and feedback! Please send comments to myl@us.ibm.com.

### **IEEE Solid-State Circuits Society AdCom**

#### President:

Richard C. Jaeger Alabama Microelectronics Center Auburn University, AL jaeger@eng.auburn.edu Fax: +1 334 844-1888

#### Vice President:

Willy Sansen K. U. Leuven Leuven, Belgium

#### Secretary:

David A. Johns University of Toronto Toronto, Ontario, Canada

#### Treasurer:

Rakesh Kumar Technology Connexions Poway, CA

#### Past President:

Stephen H. Lewis University of California Davis, CA

#### Other Representatives:

Representative to Sensors Council Darrin Young Representative from CAS to SSCS Domine Leenaerts Representative to CAS from SSCS Un-Ku Moon

#### **Newsletter Editor:**

Lewis Terman IBM T. J. Watson Research Center terman@us.ibm.com Fax: +1 914 945-4160

#### **Newsletter Coeditor:**

Mary Y. Lanzerotti IBM T.J. Watson Research Center myl@us.ibm.com Fax: +1 914 945 1358

### Elected AdCom Members at Large Terms to 31 Dec. 07:

Bill Bidermann David Johns Terri Fiez Takayasu Sakurai Mehmet Soyuer

#### Terms to 31 Dec. 08:

Wanda K. Gass Ali Hajimiri Paul J. Hurst Akira Matsuzawa Ian Young

#### Terms to 31 Dec. 09:

John J. Corcoran Kevin Kornegay Hae-Seung (Harry) Lee Thomas H. Lee Jan Van der Spiegel

#### **Chairs of Standing Committees:**

Awards David Hodges

Chapters Jan Van der Spiegel

Education CK Ken Yang

Meetings Anantha Chandrakasan

Membership Bruce Hecht

Nominations Stephen H. Lewis

Publications Bernhard Boser

For detailed contact information, see the Society e-News: www.ieee.org/portal/site/sscs

For questions regarding Society business, contact the SSCS Executive Office.

Contributions for the Spring 2007 issue of the Newsletter **must be received by 8 February 2007** at the SSCS Executive Office. A complete media kit for advertisers is available at www.spectrum.ieee.org/mc\_print. Scroll down to find SSCS

Anne O'Neill, Executive Director

IEEE SSCS

445 Hoes Lane

Piscataway, NJ 08854

Tel: +1 732 981 3400

Fax: +1 732 981 3401

Famil: sscs@ieee.org

Katherine Olstein, SSCS Administrator

IEEE SSCS

445 Hoes Lane,

Piscataway, NJ 08854

Tel: +1 732 981 3410

Fax: +1 732 981 3401

Email: sscs@ieee.org

Katherine Olstein, SSCS Administrator

IEEE SSCS

445 Hoes Lane,

Piscataway, NJ 08854

Tel: +1 732 981 3410

Fax: +1 732 981 3401

Email: k.olstein@ieee.org

©Copyright IBM Corporation 2006. All rights reserved. Reproduced by permission of IBM Corporation.

3

Winter 2007 Volume 12, Number 1

| Editor's Column      |  |

|----------------------|--|

| President's Message4 |  |

| Corrections4         |  |

20

#### **RESEARCH HIGHLIGHTS**

| Analog IC Design at the University of Twente |  |

|----------------------------------------------|--|

|----------------------------------------------|--|

#### TECHNICAL LITERATURE

| ILCHINICAL LITERATURE                                                  |

|------------------------------------------------------------------------|

| A 30 Year Retrospective on Dennard's MOSFET Scaling Paper1             |

| Device Scaling: The Treadmill that Fueled Three Decades of Semi-       |

| conductor Industry Growth                                              |

| Recollections on MOSFET Scaling                                        |

| The Business of Scaling                                                |

| A Perspective on the Theory of MOSFET Scaling and its Impact2          |

| The Impact of Scaling and the Scaling Development Environment 3        |

| It's All About Scale                                                   |

| Design of Micron MOS Switching Devices                                 |

| Ion Implanted MOSFET's with Very Short Channel Lengths3                |

| Design of Ion-Implanted MOSFET's with Very Small Physical Dimensions 3 |

|                                                                        |

#### **PEOPLE**

| An Interview with James Meindl - 2006 IEEE Medal of Honor Recipient | † 51 |

|---------------------------------------------------------------------|------|

| Hugo De Man Awarded for Leadership in Integrated Circuit Design .   | .53  |

| Yannis P. Tsividis to Receive IEEE Kirchhoff Award                  | .56  |

| IEEE Educational Innovation Award to Terri Fiez                     | .58  |

| 16 New Speakers Diversify SSCS Distinguished Lecturer Program       | .61  |

| New Senior Members                                                  |      |

| Tools: How to Write Readable Reports and Winning Proposals          | 67   |

- 4

### **CHAPTER NEWS**

| SSCS Awards \$35,000 in Chapter Subsidies                        | .69 |

|------------------------------------------------------------------|-----|

| Far East Chapters Meet in Hangzhou, China                        | .70 |

| V. Oklobdzija Offers IEEE DL Talks in Western Australia          |     |

| Denver Host's Technical Seminars on Cutting-Edge CMOS Technology |     |

CONFERENCES

| Second A-SSCC Considers Challenges for the e-Life                | .74 |

|------------------------------------------------------------------|-----|

| Solid-State Circuits Conference Will Focus on Nano-Era Synergy . | .76 |

| Invitation from the ISSCC 2007 Chair                             | .75 |

| AACD Conference Will Convene on 27-29 March 2006                 |     |

#### **NFWS**

| 11E110                                                  |     |

|---------------------------------------------------------|-----|

| SSCS AdCom Election for 2007-2009 Term                  | .80 |

| IEEE Design Council Newsletter Completes Inaugural Year |     |

| IEEE Teaching Awards                                    | .81 |

| Call for Nominations: SSCS Predoctoral Fellowships      | .82 |

|                                                         |     |

### **Message from the President**

In 2007, look for an unadvertised bonus with your SSCS membership: A free subscription to the brand new quarterly Nanotechnology Magazine. We believe that circuit experts need to be in touch with this rapidly progressing technology. Some day it will be a fruitful area

for circuits development, and opportunities to contribute will arise.

The minimal subscription cost to the Society for the launch year of the new magazine prompted the AdCom to join the Nanotechnology Council. We hope the Council's magazine effort will be of comparable interest to its Transactions on Nanotechnology, which is just beginning its sixth year and has among the highest rates of citation as measured by the Thompson ISI. I would like to receive feedback from you on how useful a tool the new magazine is. Look for the first issue in the spring of 2007.

2007 is the Society's 10th anniversary, having evolved from the Solid-State Circuits Council that originated in 1970. We've updated the SSCS logo for this year to draw attention to our progress. Since 1997, the Journal of Solid-State Circuits has increased coverage of technical articles by 40%, and the SSCS Newsletter by 2 1/2 times. The JSSC continues to be the most read in IEEE Xplore and the most cited in patents. Your SSCS membership provides online access not only to the Journal but also to the digests of our five major solid-state circuits conferences and most of their historic record. Local chapters have grown from 2 to 59, with

the recent addition of Tainan (Taiwan) and South Brazil. Celebrate our anniversary by browsing your technical articles online.

I've been active in the last quarter attending many of the conferences that SSCS cosponsors to sample their quality, focus, and differences, as well as to increase the Society's visibility and support for these important gatherings of technical experts. ESSCIRC in Montreux, Switzerland last fall was fully overlapped with the ESS-DERC device conference. One was able to move freely between the co-located meetings. The wide variety of plenary topics covered by the two meetings was of particular interest. Welcoming the Asian-Solid-State Circuits Conference in Hangzhou, China two months later, I was able to talk with circuit experts from around the world, and by the time this issue reaches you, I will have celebrated the opening of the 20th International Conference on VLSI Design in Bangalore.

Thanks to all of our members who voted in our fall election. Welcome to our new additions to AdCom, Kevin Kornegay from Georgia Tech and Harry Lee from MIT. And welcome back to returning AdCom members John Corcoran from Agilent Laboratories, Tom Lee from Stanford, and Jan Van der Spiegel from the University of Pennsylvania. The Society is beginning a review of its priorities for 2007 and beyond. As Society members, please make your interests known to your AdCom representatives. Start a conversation and help the Society point to the future that you feel is coming.

Richard C. Jaeger

### **Corrections** -

In the article entitled "Overview of CMOS Technology Development in the MIRAI Project," by Toshiaki Masuhara and Masataka Hirose in the September 2006 issue, the last sentence in the Section entitled "New Circuits and System Technology - Post-fabrication Adaptive Adjustment" contains an incorrect expression, which is corrected as in the underlined expression in the following sentence:

"As shown in Fig. 3, the developed tool successfully extracted the 34 model parameters in 23 hours with a PC and resulted in a mean RMS error of 1.83% for benchmark MOSFETs."

In the Section, "New Gate Stack Technology with High-k Materials", the caption for Figure 4 should read:

Fig. 4 Gate leakage current in MIRAI HfAlON formed by Layer-by-Layer Deposition and Annealing (LL-D&A) <sup>4</sup>).

- (a) Comparison of gate leakage current in MOSFETs with HfAlON gate insulator and HfSiON <sup>5</sup>).

- (b) Cross sectional TEM micrograph of HfAlON/SiO<sub>2</sub>/Si gate stack formed by Layer-by-Layer Deposition and Annealing.

The following corrections pertain to the reprint of "Lithography and the Future of Moore's Law" (Moore, 1995) in the September 2006 issue:

I have reproduced photomicrographs of the first planar transistor and the first commercially-available integrated circuit in Figs 3 & 4. I am particularly fond of the transistor, since it is one of the very few products that I designed myself that actually went into production.

Fig. 3. Photomicrograph of the first commercial planar transistor.

continued on page 10

## **Analog IC Design at the University of Twente**

Bram Nauta, IC Design Group, University of Twente, Enschede, The Netherlands, b.nauta@utwente.nl

#### Introduction

This article describes some recent research results from the IC Design group of the University of Twente, located in Enschede, The Netherlands.

Our research focuses on *analog* CMOS circuit design with emphasis on high frequency and broadband circuits. With the trend of system integration in mind, we try to develop new circuit techniques that enable the next steps in system integration in nanometer CMOS technology. Our research funding comes from industry, as well as from governmental organizations. We aim to find fundamental solutions for practical problems of integrated circuits realized in industrial Silicon technologies.

CMOS IC technology is dictated by optimal cost and performance of digital circuits and is certainly not optimized for nice analog behavior. As analog designers, we do not have the illusion of being able to change CMOS technology, so we have to "live with it" and solve the problems by design. In this article several examples will be shown where problematic analog behavior, such as noise and distortion, can be tackled with new circuit design techniques. These circuit techniques are developed in such a way that they do benefit from modern technology and thus enable further integration. This way we can improve various analog building blocks for wireless, wire-line and optical communication. Below some examples are given.

#### Thermal Noise Cancelling

Noise is an important issue; in communication circuits the sensitivity of the receiver is limited by the noise level of the circuits. Especially, the noise of the first amplifier in the receiving chain is of high importance, since after that amplifier the signal is stronger and the allowable noise levels are higher. For narrowband receivers the added noise of the amplifier can be reduced relatively easily. This is done by using resonant structures, built with - for example - integrated spiral inductors and capacitors which provide voltage gain of the narrowband signals and therefore needing less gain from "noisy" transistors. For wideband systems, e.g. for TV tuners, UWB (Ultra Wide Band) communication and future software defined radio, several octaves of bandwidth are needed and simple resonant structures cannot be used. For these applications, low noise gain stages using noisy transistors have to be used, which is quite a challenge. Apart from the gain and noise demands, additional demands, such as input impedance matching and good linearity, need to be satisfied.

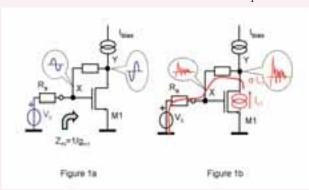

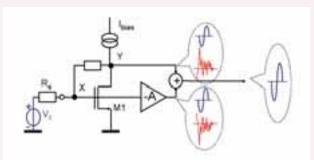

**Figure 1a** shows a wide band first amplifier stage, denoted as a common-source feedback amplifier.

Fig 1a: common source LNA with impedance matching, the signals at nodes X and Y have opposite sign. Fig 1b: The noise of M1 generates in-phase noise voltages at nodes X and Y.

The input impedance is  $1/g_m$  of M1, and must be equal to the source impedance Rs, usually 50 Ohms. With this in mind the gm of M1 is fixed by design resulting in poor noise behavior of the amplifier: The "noise figure" is always larger than 3dB. In order to reduce the noise one would like to increase the  $g_m$  of M1 (preferably  $g_m >> 1/Rs$  for minimal noise figure) but then the input impedance does not match anymore. Conventionally, additional feedback techniques are used to break this paradox, but at the cost of stability and bandwidth issues.

PhD Student Federico Bruccoleri realized, however, that generated noise can be cancelled by proper circuit design. If we take a look at **Figure 1b**, we can see how the noise current of M1 flows in the circuit; this is indicated by the red arrow.

The noise current due to M1 flows in a loop, through Rs. This noise current generates a noise voltage at nodes X and Y which are of different magnitude but of *the same phase*. The signals nodes X and Y are in anti-phase due to the inverting nature of this amplifier. So somehow it should be possible to separate the signal from the noise!

By adding an additional amplifier "A," as shown in **Figure 2**, we can construct an output signal in such a way the wanted signals at nodes X and Y are added and that the noise at nodes X and Y are cancelled [1]. This way we can cancel the noise of M1, which holds for both thermal and 1/f noise. Of course amplifier "A" will now add additional noise, but this needs not to be a problem. The reason for this is that in contrast to M1, we can choose the gm of the input stage of amplifier "A" relatively large, and thus make it low-

5

Fig 2: Basic idea of noise cancelling; the noise due to M1 is cancelled.

noise. So we don't break the laws of physics: we still have to burn power (in amplifier "A") to get a lownoise amplifier, but we have created a degree of freedom by decoupling the input matching ( $g_{m1}$ =1/Rs) and allowing a large gm ( $g_{mA}>>1/Rs$ ) in the amplifier A. The noise of  $I_{bias}$  is cancelled as well. A prototype amplifier has been realized on silicon and it worked well: the noise figure was well below 3dB, which proves the concept of noise canceling. Also the robustness to mismatch in the two noise paths is good [1]. Other topologies are also possible offering "balun" functionality [1,2].

#### Low Frequency noise reduction in MOSFETS

Low frequency (LF) transistor noise, also denoted as 1/f noise, is of great importance in today's circuit design. Especially, baseband circuits suffer from this noise phenomenon which can be dominant well above 10MHz. Also high-frequency oscillators suffer from LF noise, since this noise is up-converted and appears close to the carrier frequency of the oscillator degrading the close-in phase noise.

A while ago, a MSc student Gian Hoogzaad did calculations on the phase noise of CMOS inverter-based ring oscillators. These oscillators were free running, and we expected a large close-in phase noise due to the low frequency noise of the MOS-FETs in the oscillator. Measurements, however, showed a much lower, (8dB less), close-in phase noise than we expected from the LF noise of those single transistors. The student and his supervisor Sander Gierkink were very confident of his calculations, and we were thus wondering what caused the 8dB lower close-in phase noise.

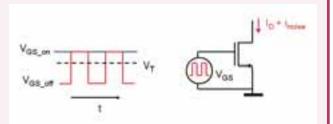

Finally, we suspected that the large signal switching behavior in the inverters caused the strange effect and we carried out measurements on stand-alone transistors under normal bias and under "switched bias". **Figure 3** illustrates these conditions.

One would expect 6 dB less noise from the switched bias transistors compared to the normal one: 3dB reduction due to the 50% duty-cycle of the noise and another 3dB due to up-conversion of the LF noise.

Fig. 3: MOSFET under constant bias (blue) and switched bias (red)

Measurements however showed 6 + 8 = 14 dB reduction for frequencies lower than the switching frequency, as illustrated with the red curve in **Figure 4**.

This matched to the 8dB reduction of phase noise in the inverter ring-oscillator. This reduction takes place for frequencies lower than the switching frequency. Later, we discovered that a similar noise phenomenon had been observed before in physicists' device experiments[3]; however, we could not find a citation to this paper.

Fig. 4: Measured LF noise of a MOSFET under constant bias (blue), expected 6 dB reduction under switched bias (red dashed curve) and measured behavior with intrinsic reduced noise (red)

So, in fact, all inverter based ring oscillators benefited already from this phenomenon while none of the designers apparently realized this. To a large extent this is because the "switched bias" noise reduction is not modeled in today's simulators. Also, the effect can be masked by the very large spread which is normally present in LF noise, especially for small area devices.

After a study carried out in the PhD projects by Arnoud van der Wel and Jay Kolhatkar, the phenomena could be explained by the bias dependency of the emission and capture time constants which are responsible for the trapping and de-trapping of oxidecharge in MOSFETs. This trapping and de-trapping

causes so-called random telegraph signals, which determine the low frequency noise of the transistors. The reduction effect is found to be present in all technologies investigated: from  $10\mu m$  down to  $0.12\mu m$ , both N and P MOSFETs and works for switching frequencies up to at least 3GHz.

For large-geometry transistors we generally see a significant reduction, whereas for very small-sized modern devices the noise can decrease but also increase. This is due to the very small number of traps in the transistors (sometimes only one trap) while the phenomenon depends strongly on the energy distribution of the traps. Details can be found in [4].

Other known techniques to reduce the effect of LF noise in electronic circuits are chopping and correlated double sampling. The LF noise can also be reduced by increasing gate area of the MOSFETS, at the cost of area and/or power consumption. The switched bias technique offers an orthogonal method to reduce the intrinsic LF noise in the transistor itself. It is beneficial especially in circuits where switching already occurs, such as oscillators and discrete time circuits.

## Distortion Cancelling using Poly-Phase Technique

In deep submicron technology, distortion becomes an increasing problem. Large signals are required for dynamic range reasons or simply because for a given radio standard dictates the output power to be delivered by a power amplifier. The transistors, however, have less voltage gain and exhibit very non-linear behavior, which makes linear circuit design a challenge.

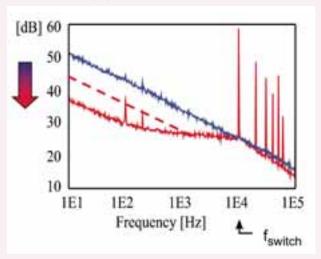

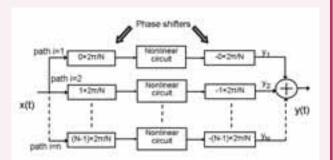

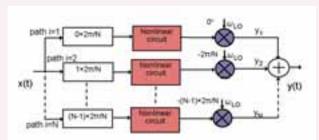

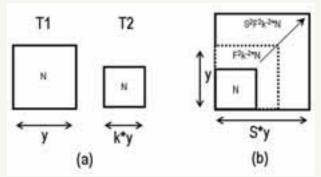

We know that in differential circuit the even harmonics are cancelled if the signals are in anti-phase. With this in mind, MSc student Eisse Mensink investigated whether it would be possible to use more than 2 paths and multiple phases of the signal (poly-phase) and cancel more than 2 harmonics. The basic idea is shown in **Figure 5**, where the signal path is split in N separate parallel paths.

N=2 equals the well-known differential circuit topology to cancel even harmonics. If phase shifters are available before and after the nonlinear circuit, the structure of Fig. 5 can cancel the harmonics up to N-1 [5]. The problem is however that wide-band phase shifters are very hard to implement with analog circuits. For this reason, we choose to use mixers as second phase shifters, as shown in **Figure 6**.

The mixers each have a Local Oscillator (LO) input with each a different phase, equally divided over 360/N degrees. Since we automatically get up-conversion of our input signal with these mixers, we strategically changed our plan and decided to build an RF

Fig. 5: N path poly-phase circuit can cancel up to the N-1<sup>th</sup> harmonic.

power up-converter. In this up-converter the first phase shifters are assumed to be implemented in the digital baseband, while in the up-conversion mixers all problematic harmonics due to nonlinearities of the N power amplifier stages can be cancelled via the poly-phase technique in combination with a 1/3 duty-cycle LO-signal [6].

A silicon realization, designed by MSc Student

Fig 6: Wide band phase shifters can be implemented with mixers, resulting in up-converter behavior.

Rameswor Shrestha, is based on the circuit of Fig. 7 with N=18 [6]. The colors in **Figure 7** correspond to the colors of the functional blocks of Figure 6.

Rameswor demonstrated a power up-conversion mixer, which is driven in compression while all harmonics and their sidebands, up to the 17th harmonic, still remain under -40dBc. Without this poly-phase topology (i.e. for N=1) the harmonics would be below only -6dBc, which clearly demonstrates the effectiveness of the technique - 34 dB improvement. The RF frequency could be varied from DC to 2.5GHz and the final accuracy of the technique was limited by timing of the LO phases.

Conventional RF up-converters require expensive post-filters, dedicated for every RF frequency to filter out the harmonics and sidebands in order to satisfy the radio transmit mask. With this poly-phase up-converter the harmonics can be rejected and the filter demands can be much relaxed. Applications of this poly-phase up-converter can probably be found in wide band flexible up-converters and software radio transmitters, where the actual RF frequency is a priori

7

Fig 7: Basic circuit of Power up-converter.

not known and is free to be chosen in a given range.

#### **Pulse Width Modulation Cable Equalizer**

For digital data communication over copper cables, electronic equalizer circuits are used to compensate for the losses and reflections over the cables. Thanks to these electronic circuits, higher data rates can be achieved over relatively cheap cables. Examples are USB and LAN.

A well known technique used at the transmitter side is pre/de-emphasis, effectively high-pass filtering the transmitted signal. This way the low-pass characteristic of the cable is compensated for. These transmit pre-emphasis filters are generally implemented with Finite Impulse Response (FIR) filters, most often with just a few symbol spaced taps.

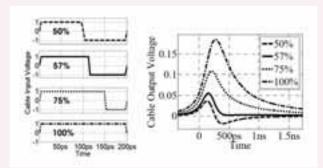

As an alternative to FIR filters Daniel Schinkel and Jan-Rutger Schrader proposed Pulse Width Modulation (PWM) on a digitally coded signal [7,8]: If a '1'-bit has to be transmitted, a 1-0 pattern is transmitted in one bit time and if a '0'-bit has to be transmitted a 0-1 pattern is transmitted in one bit time. This is similar to Manchester coding but with adjustable, non-50% duty-cycle. The duty-cycle of the 1-0 and 0-1 pattern is chosen in such a way that it compensates for the cable loss. This is illustrated in **Figure 8**, where the duty-cycle of a 1-0 pattern is varied and the corresponding cable responses are plotted.

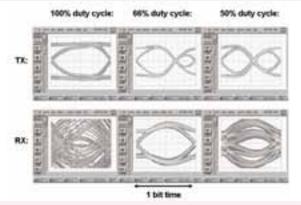

Thus, by changing the duty-cycle, the transmitted spectrum, in which the lower frequencies are attenuated, is tuned for the high-frequency loss of the cable. In a real application an adaptive loop with return-channel communication takes care for this tuning, similar as in a conventional FIR approach. A test chip achieved 5Gb/s over 25m of RG-58U coaxial cable

which has a loss of 33 dB at the Nyquist frequency of 2.5GHz [8] . The eye diagram for various duty-cycles is shown in **Figure 9**: for this 10m long cable 66% is the optimum duty-cycle.

The PWM technique can compensate for higher loss compensation (33 dB in contrast to approximately 20dB for 2 tap symbol-spaced FIR) because the resulting spectrum has a better match to the skin-

Fig. 8: Transmitting a "1" using PWM pre-emphasis: tuning the duty-cycle of the 1-0 pattern can compensate for the cable response.

effect and dielectric loss of the cable. Still only one tuning "knob" is required to fit the transfer function to the cable. Moreover the technique is insensitive to slew-rate distortion and requires only two discrete amplitudes at the TX output (with a continuously adjustable duty-cycle), which makes it suitable for modern CMOS technologies. The technique was also successfully applied earlier for very long on-chip RC limited interconnects by Daniel Schinkel and Eisse Mensink [7].

Fig 9: 5Gb/s eye patterns of transmitted signals (TX) and received signals (RX) for duty-cycle settings of 100% (normal data), 66% (optimal PWM) and 50% (overcompensated PWM) over 10m RG-58CU cable.

#### **Optical Detectors in Standard CMOS**

Traditionally, in optical communication extremely high data rates have to be achieved over long distances. Therefore optical communication is the domain of expensive exotic technologies and the high

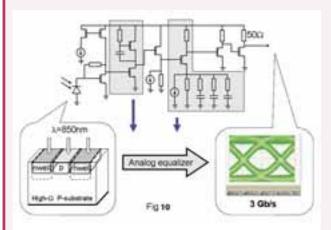

costs associated with it can be shared between many users. For optical communication over short distances (meters) or very short distances (optical interconnect), cost issues, however, do play a crucial role. Therefore, we started a project to integrate an optical detector in standard CMOS technology; the optical data signal can now shine directly on a digital CMOS chip. Due to the availability of low-cost high-speed laser at 850nm wavelength and the compatibility with both inexpensive plastic fibers and with photo-generation in silicon, our work mainly uses this 850nm.

An essential part of an optical detector in CMOS is the integrated photodiode structure, shown in the leftmost inset in **Figure 10**.

Fig. 10: Transmitting a "1" using PWM pre-emphasis: tuning the duty-cycle of the 1-0 pattern can compensate for the cable response.

Incident photons are absorbed in the silicon at tens of microns deep, much deeper than any junction in standard CMOS. In the absorption process, electrons and holes are generated and most of them slowly diffuse to the pn-junctions where the actual detection takes place. The slow diffusion causes the -3dB bandwidth of the photodiode to be in the order of 5 MHz, which causes a serious speed problem. In literature authors generally modify the technology, e.g. to allow high voltages and very wide depletion layers to boost the speed of the carriers, however this implies that non-standard CMOS has to be used. The maximal speed reported in standard CMOS so far has been 700Mbit/sec.

Ph.D. student Sasa Radovanovic implemented another solution. Although the -3dB frequency is very low, the roll-off per decade of frequency appears to be very low as well; only 3 to 4 dB per decade, up to in the low GHz region. Therefore, Sasa used an analog equalizer, with opposite frequency characteristic after the transimpedance amplifier following the diode to get a flat overall response up to a few GHz. One might assume that the production spread in time constants between the equalizer and the diode itself might ruin the performance, but

thanks to the low roll off, even +/- 20% spread in time constants hardly affects the time pulses. The resulting chip achieved 3Gbit/sec in standard 0.18 $\mu$ m CMOS, with a BER of 10<sup>-11</sup> at an optical input power of 25 $\mu$ W [9]. The speed limitation was in the electronic circuit, and is expected to scale with technology. This result enables high speed optical inputs for standard CMOS chips.

#### Conclusion

Several examples of new design methodologies have been illustrated. These methodologies benefit from modern CMOS technology and may be helpful for future system integration. More work can be found at the URL: http://icd.ewi.utwente.nl

#### **Acknowledgements**

The work described in this article has been carried out by many students; however, without the supervision or help from Eric Klumperink, Anne Johan Annema, Ed van Tuijl, Ronan van der Zee, Gerard Wienk and Henk de Vries, these results would not have been here. This work has been funded by: STW, FOM and MESA\*. Philips and CERN are acknowledged for providing silicon access.

#### References

- [1] F. Bruccoleri, E.A.M. Klumperink, B. Nauta, "Wide-Band CMOS Low-Noise Amplifier Exploiting Thermal-Noise Canceling", IEEE Journal of Solid-State Circuits, Vol. 39, No. 2, pp. 275 -282, February 2004.

- [2] S. Chehrazi, A. Mirzaei, R. Bagheri, A. A. Abidi; "A 6.5 GHz wideband CMOS low noise amplifier for multi-band use", 2005 IEEE Custom Integrated Circuits Conference18, pp. 801 804, September 2005.

- [3] I. Bloom and Y. Nemirovsky, "1/f noise reduction of metal-oxide semiconductor transistors by cycling from inversion to accumulation", Applied Physics Letters, vol. 58, no. 15, pp. 1664–1666, Apr. 1991.

- [4] A.P. van der Wel, E.A.M. Klumperink, J. Kolhatkar, E. Hoekstra, M. Snoeij, C. Salm, H. Wallinga and B. Nauta "Low Frequency Noise Phenomena in Switched MOSFETs", IEEE Journal of Solid State Circuits, Vol. 42, No.3, March 2007.

- [5] E. Mensink, E.A.M. Klumperink, B.Nauta, "Distortion Cancellation by Polyphase Multipath Circuits," IEEE TCAS-I, pp. 1785-1794, Sept. 2005.

- [6] R. Shrestha, E.A.M. Klumperink, E. Mensink, G. Wienk, B. Nauta, "A Polyphase Multipath Technique for Software Defined Radio Transmitters", IEEE Journal of Solid State Circuits, Vol. 41, No.12, Dec 2006.

- [7] D. Schinkel., E. Mensink, E.A.M. Klumperink, A.J.M. van Tuijl, B. Nauta, "A 3Gb/s/ch Transceiver

9

[8]

for 10-mm Uninterrupted RC-Limited Global On-Chip Interconnects", IEEE Journal of Solid State Circuits, Vol. 41, No. 1, pp. 297- 306, Jan. 2006.

J.H.R. Schrader, E.A.M. Klumperink, J.L. Visschers, B. Nauta, "Pulse-Width Modulation Pre Emphasis applied in a Wireline Transmitter, achieving 33dB Loss Compensation at 5-Gb/s in

0.13- $\mu$ m CMOS", IEEE Journal of Solid-State Circuits, Vol. 41, No. 4, pp.990-999, April 2006.

[9] S. Radovanovic, A.J. Annema, B. Nauta, "A 3 Gb/s optical detector in standard CMOS for 850 nm optical communication" IEEE Journal of Solid-State Circuits, Volume 40, No.8, Pg:1706 -1717, Aug. 2005.

#### **About the Author**

Bram Nauta was born in Hengelo, The Netherlands. In 1987 he received the M.Sc degree (cum laude) in electrical engineering from the University of Twente, Enschede, The Netherlands. In 1991 he received the Ph.D. degree from the same university on the subject of

analog CMOS filters for very high frequencies.

In 1991 he joined the Mixed-Signal Circuits and Systems Department of Philips Research, Eindhoven the Netherlands, where he worked on high speed AD converters and analog key modules. In 1998 he returned to the University of Twente, as full professor heading the IC Design group, which is part of the

CTIT Research Institute. His current research interest is high-speed analog CMOS circuits. Besides, he is also part-time consultant in industry and in 2001 he co-founded Chip Design Works.

His Ph.D. thesis was published as a book: Analog CMOS Filters for Very High Frequencies, (Springer, 1993) and he received the "Shell Study Tour Award" for his Ph.D. Work. From 1997-1999 he served as Associate Editor of IEEE Transactions on Circuits and Systems -II; Analog and Digital Signal Processing, and in 1998 he served as Guest Editor for IEEE Journal of Solid-State Circuits. From 2001 to 2006 he was Associate Editor for IEEE Journal of Solid-State Circuits and he is also member of the technical program committees of ISSCC, ESSCIRC, and Symposium on VLSI circuits. He is co-recipient of the ISSCC 2002 "Van Vessem Outstanding Paper Award."

### **Corrections** continued from page 4

Fig. 4. Photomicrograph of one of the first planar integrated circuits produced by Fairchild Semiconductor in the early 1960's.

The unusual diameter of 764 microns was chosen because we were working in English units and that is thirty thousandths of an inch, or 30mils. The minimum feature size is the three mil metal line making the circular base contact. Metal-to-metal spacing is five mils to allow the 2.5mil alignment tolerance we needed.

Interestingly enough at the time the idea for the planar transistor was conceived by Jean Hoerni in the early days of Fairchild Semiconductor, it had to sit untried for a couple of years, because we did not have the technology to do four aligned mask layers. In fact, we were developing the technology to do two aligned oxide-masked diffusions plus a mesa etching step for transistors. The original step and repeat camera that Bob Noyce designed using matched 16mm movie camera lenses had only three lenses, so it could only step a three-mask set. We had to wait until the first mesa transistors were in production before we could go back and figure out how to make a four mask set to actually try the planar idea.

The first integrated circuit on the graph is one of the first planar integrated circuits produced. It included four transistors and six resistors.

It has always bothered me that the picture of this important device that got preserved was of the ugly chip shown in Fig. 4. The circuit had six bonding pads around the circumference of a circle for mounting in an 8-leaded version of the old TO-5 outline transistor can. In this case only six of the eight possible connections were required. We did not think we could make eight wire bonds with reasonable yield, so for these first integrated circuits we etched a round die that let us utilize blobs of conducting epoxy to make contact to the package pins. For the die in the picture, the etching clearly got away from the etcher.

A prior version of "The Mythology of Moore's Law," by Tom R. Halfhill in the September 2006 issue was published in Microprocessor Report of December, 2004.

# A 30 Year Retrospective on Dennard's MOSFET Scaling Paper

Mark Bohr, Intel Corporation, mark.bohr@intel.com

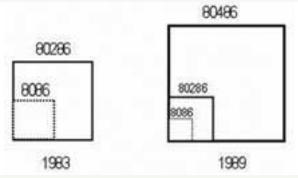

ore than three decades have passed since the team of Robert Dennard, Fritz Gaensslen, Hwa-Nien Yu, V. Leo Rideout, Ernest Bassous and Andre LeBlanc from the IBM T. J. Watson Research Center wrote the seminal paper describing MOSFET scaling rules for obtaining simultaneous improvements in transistor density, switching speed and power dissipation [1]. At the time of this paper (1974), commercially available circuits were using MOSFETs with gate lengths of approximately 5 microns, but devices with shorter gate lengths were already being built in laboratories that were demonstrating the benefits of further scaling. The scaling principles described by Dennard and his team were quickly adopted by the semiconductor industry as the roadmap for providing systematic and predictable transistor improvements.

Table I is reproduced from Dennard's paper and summarizes transistor or circuit parameter changes under ideal scaling conditions, where  $\kappa$  is the unitless scaling constant. The tantalizing benefits of MOSFET device scaling immediately leap out from this table: as transistors get smaller, they can switch faster and use less power. But of course learning exactly bow to make transistors smaller in a way that could be done practically in high volume manufacturing would take time. It would take time to develop lithographic techniques to pattern smaller feature sizes, to grow thinner gate oxides, and to reduce defect levels at these increasingly challenging dimensions. But this paper gave our industry a roadmap, a method for setting targets and expectations for coming generations of process technology. This paper gave us the more specific transistor scaling formula needed to continue Moore's Law, which was first articulated in a paper by

Gordon Moore in 1965 and was in effect being followed by the semiconductor industry since the early 1960's. (To read reprints of Gordon Moore's 1965 and 1975 papers along with recent commentaries on Moore's Law, see the September 2006 issue of the *IEEE Solid-State Circuits Society Newsletter.*)

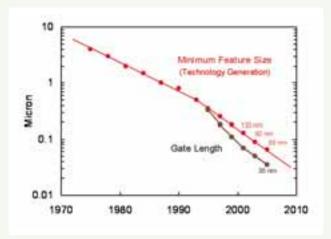

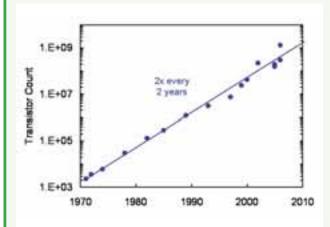

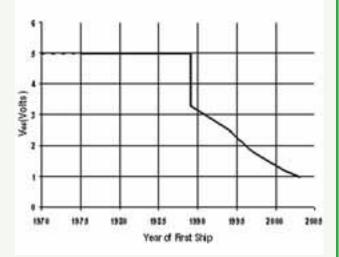

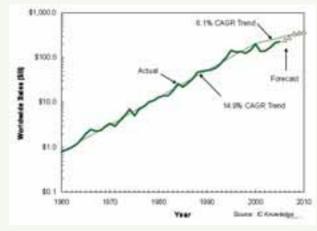

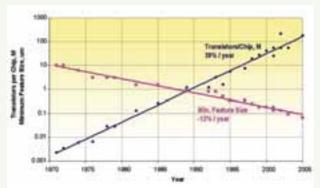

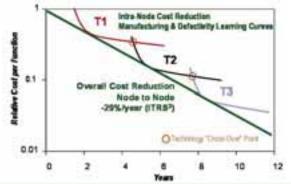

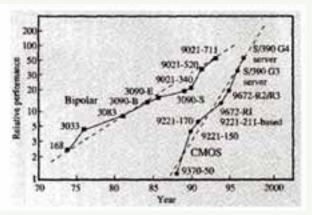

The ideas described in Moore's and Dennard's papers set our industry on a course of developing new integrated circuit process technologies and products on a regular pace and providing consistent improvements in transistor density, performance and power. Each new generation of process technology was expected to reduce minimum feature size by approximately 0.7x ( $\kappa$ ~1.4). A 0.7x reduction in linear features size was generally considered to be a worthwhile step to take for a new process generation as it provided roughly a 2x increase in transistor density. During the 1970's and 1980's the semiconductor industry was introducing new technology generations approximately every 3 years. This translates to transistor density improvements of ~2x every 3 years, but this was also a period when average chip sizes were increasing, resulting in transistor count increases of close to 4x every 3 years (or 2x every 18 months). Starting in the mid-1990's our industry accelerated the pace of introducing new technology generations to once every 2 years and that pace continues to this day (see Figure 1). The trend of increasing chip size has slowed due to cost constraints, so we have settled into a trend of roughly doubling transistor density and transistor count every 2 years (see Figure 2).

Even more surprising, from a MOSFET scaling perspective, is that over the past 10 years MOSFET gate lengths have been scaling faster than other minimum feature sizes (see Figure 1). Prior to the mid-1990's,

Table I: Scaling Results for Circuit Performance (from Dennard)

| Device or Circuit Parameter  | Scaling Factor |

|------------------------------|----------------|

| Device dimension tox, L, W   | 1/ĸ            |

| Doping concentration Na      | ĸ              |

| Voltage V                    | 1/ĸ            |

| Current I                    | 1/k            |

| Capacitance &4/t             | 1/K            |

| Delay time/circuit VC/I      | 1/ĸ            |

| Power dissipation/circuit VI | $1/\kappa^2$   |

| Power density VI/A           | 1              |

Figure 1: Feature size scaling for Intel logic technologies

11

Figure 2: Transistor count trend for Intel microprocessors

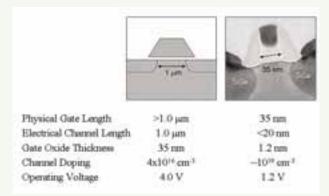

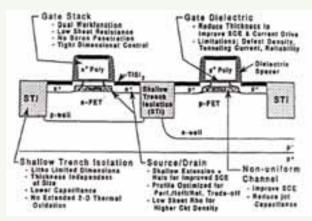

gate lengths were roughly the same size as other minimum process features, but starting with the 0.35 µm generation, gate lengths have been scaling faster than 0.7x per generation to realize performance advantages, even though gate pitch has been scaling at the normal rate. This has been a key factor in microprocessors achieving >3 GHz operating frequencies sooner than most experts thought possible even 10 years ago. It is exciting to see in Figure 3 how far we have taken Dennard's scaling law by comparing the 1 mm transistor described in his 1974 paper to the 35 nm gate length transistor used in Intel's 65 nm generation logic technology that started high volume manufacturing in 2005 [2]. The Intel transistor shown in Figure 3 provides an example of an emerging trend among semiconductor manufacturers: the introduction of new structures and materials to extend transistor scaling. In this case the new feature is selectively deposited SiGe source-drains to provide strained silicon for improved transistor performance [3].

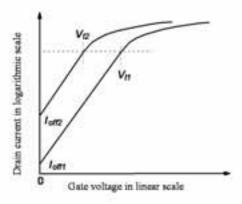

Just as there have been questions about the end of Moore's Law, there have also been questions about the end of MOSFET scaling. In both cases, the answer is that the end is not yet in sight, although we face growing challenges in their continuation. Voltage scaling has been an extremely important component of MOSFET scaling because it maintains constant electric field, which is important for reliability, and it lowers transistor power, which is needed to maintain constant power density. But even in the early days of MOSFET scaling it was difficult to follow ideal voltage scaling requirements because of the need to use industry standard voltages, such as 12V, 5V, 3.3V, etc. Eventually we were able to deviate from standard voltage levels on key products such as microprocessors and were free to adjust product voltage levels to meet specific performance and power targets. More recently, however, voltage scaling has run into lower limits imposed by threshold voltage (V<sub>T</sub>) scaling limits [4]. Dennard's scaling law assumed that  $V_{\scriptscriptstyle T}$  would scale along with operating voltage, and thus provide

Figure 3: MOSFET structure from Dennard's 1974 paper (left) and from Intel's 65 nm generation logic technology in 2005 (right)

improved performance and power. But this 1974 work ignored the impact of transistor sub-threshold leakage on overall chip power. Sub-threshold leakage was relatively low in the 1970's and was a tiny contributor to total power consumption on logic circuits. But after 30 years of scaling,  $V_{\scriptscriptstyle T}$  has scaled to the point where sub-threshold leakage has increased from levels of <10-10 amps/mm to >10-7 amps/ $\mu$ m. Due to leakage constraints, it will be difficult to further scale  $V_{\scriptscriptstyle T}$  and thus it will also be difficult to scale operating voltage.

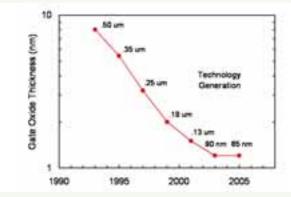

Another key assumption in Dennard's scaling law was the ability to scale gate oxide thickness. Gate oxide scaling has been a key contributor to scaling improvements over the past 30 years, but this trend is also slowing due to leakage constraints (see Figure 4). Intel's 65nm generation transistors use a SiO<sub>2</sub> gate dielectric with a thickness of 1.2 nm [2]. This dielectric is only about 5 silicon atomic layers thick and represents what is likely the limit to which SiO<sub>2</sub> can be scaled. Not only are we running out of atoms, but gate oxide leakage due to direct tunneling current is becoming a noticeable percentage of overall chip power.

Dennard's scaling law assumed that channel doping concentration could be continually increased to enable shorter channel lengths with the appropriate  $V_{\rm T}$ . When channel doping concentration gets too high

Figure 4: Gate oxide thickness trend for Intel logic technologies

Figure 5: Copper interconnects with low-\_ dielectrics from Intel's 65 nm logic technology

two problems occur: 1) carrier mobility and performance degrade due to increased impurity scattering, 2) source and drain junction leakage increases due to direct band-band tunneling. Junction leakage is already a limiter for ultra-low power integrated circuits and will eventually be a limiter for mainstream microprocessor products.

Although Dennard's paper is best known for articulating MOSFET scaling rules, less noticed was the paper's description of interconnect scaling results, as reproduced here in Table II. The key point of this table is that scaled interconnects, unlike scaled transistors, do not speed up. Scaled interconnects provide roughly constant RC delays because the reduction in line capacitance is offset by an increase in line resistance. This was not much of a concern in 1974 when interconnect delay was typically a small portion of circuit clock cycle times. But more modern logic technologies have been wrestling with the constraints imposed by interconnect delay and interconnect density [5], and have been addressing these constraints by adding more metal layers, converting from aluminum to more conductive copper wires, and replacing SiO, dielectrics with low-k dielectrics to reduce capacitance (see Figure 5).

As briefly described above, scaling transistors beyond the 65 nm generation will clearly have more challenges to contend with. It is also commonly recognized that following the simple scaling rules described by Dennard and his team back in 1974 is now no longer a sufficient strategy to meet future transistor density, performance, and power requirements. But ours is a very inventive industry and new transistor technologies such as strained silicon, high-κ

**Table II: Scaling Results for Interconnect Lines (from Dennard)**

| Parameter                                  | Scaling Factor |

|--------------------------------------------|----------------|

| Line resistance, $R_L = \rho L W t$        | ĸ              |

| Normalized voltage drop IR <sub>t</sub> /V | / к            |

| Line response time $R_LC$                  | 1              |

| Line current density I/A                   | ĸ              |

dielectrics, metal gates and multiple-gate devices have been or will be introduced to continue scaling. So although the letter of "Dennard's Law" can no longer be followed, it has gotten us very far over the past 30 years and the spirit is alive and well in transistor R&D facilities around the world.

#### References

- [1] R. Dennard, et al., "Design of ion-implanted MOSFETs with very small physical dimensions," *IEEE Journal of Solid State Circuits*, vol. SC-9, no. 5, pp. 256-268, Oct. 1974.

- [2] P. Bai, et al., "A 65nm logic technology featuring 35nm gate lengths, enhanced channel strain, 8 Cu interconnect layers, low-k ILD and 0.57 μm<sup>2</sup> SRAM cell," *International Electron Devices Meeting Technical Digest*, pp. 657-660, 2004.

- [3] K. Mistry, et al., "Delaying forever: Uniaxial strained silicon transistors in a 90nm CMOS technology," *Symposium on VLSI Technology Digest of Technical Papers*, pp. 50-51, 2004.

- [4] Y. Taur and E. Nowak, "CMOS devices below 0.1 μm: How high will performance go?" *International Electron Devices Meeting Technical Digest*, pp. 215-218, 1997.

- [5] M. Bohr, "Interconnect scaling The real limiter to high performance ULSI," *International Electron Devices Meeting Technical Digest*, pp. 241-244, 1995.

#### **About the Author**

Mark Bohr is an Intel Senior Fellow and Director of Process Architecture and Integration. He is a member of Intel's Logic Technology Development group located in Hillsboro, Oregon, where he is responsible for directing process development activities for Intel's advanced logic technologies.

13

He joined Intel in 1978 and has been responsible for process integration and device design on a variety of process technologies for dynamic RAM, static RAM and microprocessor products. He is currently directing development activities for Intel's 32 nm logic technology.

Bohr was born in Chicago, Illinois in 1953. He received the B.S. degree in industrial engineering in 1976 and the M.S. degree in electrical engineering in 1978, both from the University of Illinois, Urbana-Champaign. In 1998 he received the Distinguished Alumnus Award from the University of Illinois department of Electrical and Computer Engineering. Bohr is a Fellow of the Institute of Electrical and Electronics Engineers and was the recipient of the 2003 IEEE Andrew S. Grove award. In 2005 he was elected to the National Academy of Engineering. He holds 42 patents in the area of integrated circuit processing and has authored or co-authored 40 published papers.

# **Device Scaling: The Treadmill that Fueled Three Decades of Semiconductor Industry Growth**

Pallab Chatterjee, i2 Technologies, Inc.

In 1974 Robert Dennard, etal<sup>1</sup>, wrote a paper that explored different methods of scaling MOS devices, and pointed out that if voltages were scaled with lithographic dimensions, one achieved the benefits we all now assume with scaling: faster, lower energy, and cheaper gates. The lower energy per switching event exactly matched the increased energy by having more gates and having them switch faster, so in theory the power per unit area would stay constant. This set of linear scaling principles of MOS technology has served as the treadmill on which the entire Semiconductor Industry has grown for the past three decades.

#### Scaling in the 70's: The Era of NMOS Dynamic Random Access Memories

The late 70's NMOS based DRAMs led the technology scaling charge in a world that was still largely bipolar and dominated by TTL logic chips. The first rounds of the application of scaling theory were focused on DRAMs. Unique clock design schemes for DRAMs devised at Mostek and technology from Intel and IBM ushered in the 16k bit VLSI DRAM, the pride of the late 70's.

Japan's MITI created the VLSI Technology Project<sup>2</sup>, a consortium of five top Japanese microelectronics companies: Hitachi, NEC, Fujitsu, Mitsubishi and Toshiba. This consortium developed a complete technology infrastructure for the 256K DRAM and launched into the 1 micron VLSI era with strong progress in ultra clean technologies which gave Japan the lead in VLSI manufacturing in the early 80's.

#### The Early 80's: Crossing the Micron Barrier

Even though the scaling charge was led by NMOS, power and ease of design considerations favored CMOS Technology as the industry workhorse. The world, however, was stuck at the TTL voltage and logic level standard or 5V. The resistance to scaling voltage in the early 80's from system designers backed into the semiconductor world. This led me to propose a quasi constant voltage scaling<sup>3</sup>. The emergence of voltage tolerant device structures like the lightly dope drain (LDD) transistor, silicide clad source drain, and hot electron defense resulted from this. These technologies provided some of the keys to continue scaling feature sizes slower than voltage and continuing the treadmill for the Semiconductor Industry.

# ASIC and CAD Transforms the Chip Design Industry

Carver Meade and Lynn Conaway in their classic book, 'Introduction to VLSI Systems', used the notion

of linear relationships between different device geometries to simplify the "design rules" that abstracted the manufacturing constraints from design. Linear device scaling theory also allowed simplification of a very complex interaction of process and device physics with design.

Device models to represent the complex physics of CMOS devices in circuit simulators, like SPICE, provided the abstraction between circuit theory and device physics. Based on these abstractions the industry was able to rapidly develop design tools and systems. The University of California, Berkeley<sup>4</sup> was a leader in developing a suite of design tools that connected logic level design to circuit design to physical design and verification tools to check for design rules. The entire ASIC world of semi-custom chips opened up based on this set of abstractions and made scaling applicable to all chips.

# The Emergence of TCAD: Systematic Technology Design

The notion of creating generations of process technology that could be used for a variety of applications was emerging simultaneously with the ASIC movement to systematize chip design. Linear scaling factors began to be used as the names of the generation of technology and an informal time table started being discussed across the industry. A team at Stanford University initiated a whole new field of technology CAD<sup>5</sup> with Process Simulators and Device Simulators. This allowed systematic design of process and devices using formal design of experiment methods.

Manufacturing yield and defect analysis did not come under the purview of scaling theory and threatened to stop the scaling treadmill. Redundancy and repair techniques based on laser links were the initial answer to continue memory scaling beyond 256 Kbit. This was followed by yield analysis tools that were developed at Carnegie Mellon University<sup>6</sup>. Defect measurement tools offered by KLA, systematic yield analysis and ramp processes made the technology treadmill continue to move down the linear scaling path.

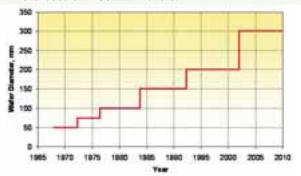

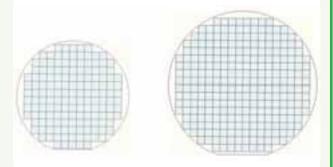

#### Single Wafer Manufacturing Systems for Scaling to Larger Wafers with Sub Half Micron Features

From 1988 through 1993 Texas Instruments partnered with DARPA, the U.S. Air Force, semiconductor equipment makers, and university researchers in the Microelectronics Manufacturing Science and Technology (MMST) Program<sup>7</sup>. Its purpose was to develop advanced IC manufacturing technologies enabling dramatic

15

improvements in process control, cycle-time, and overall flexibility and continue the scaling of devices to deep submicron to cost effectively. In particular, the MMST Program demonstrated the technical feasibility of 100% single-wafer processing, dynamic/object-oriented Computer-Integrated-Manufacturing (CIM), real-time/model-based process control, in-situ sensors, 95% dry processing, and integrated mini environments.

At that time, state-of-the-art commercial wafer fabs used a mix of approximately 60% single-wafer and 40% batch processing equipment. Since then, complete sets of commercial single-wafer process tools have become available and are the norm for deep submicron manufacturing.

The most significant contribution of MMST to single-wafer processing was in the area of Rapid Thermal Processing (RTP). In contrast to large furnaces for thermal processing, the MMST program developed processing chambers in which single wafers were heated by lamps under multi-zone, closed-loop wafer-

temperature control. Some of the initial MMST work on RTP lamps was performed in collaboration with Stanford University. Applied Materials, Inc. subsequently introduced RTP on their Centura HT™ cluster tool. MMST also created the first lithography cluster tool and the concept of the vacuum carrier which is more popularly knows as the SMIF box.

#### **SIA Industry Roadmap**

In November 1992, 179 of the key semiconductor technologists of the US gathered in Irving, Texas for a historic workshop to create a common vision for the course of the semiconductor industry for the next 15 years based on scaling technology<sup>8</sup>. The group consisted primarily of scientists and engineers from the US Semiconductor Industry and a liberal sprinkling of academics, government agencies and national laboratories. The workshop, sponsored by the Semiconductor Industry Association and coordinated by Semiconductor Research Corporation and Sematech, created the roadmap below.

1992 SIA Overall Roadmap Technology Characteristics

|                                                           | 1992       | 1995       | 1998        | 2001        | 2004        | 2007         |

|-----------------------------------------------------------|------------|------------|-------------|-------------|-------------|--------------|

| Feature Size (µm)                                         | 0.5        | 0.35       | 0.25        | 0.18        | 0.12        | 0.10         |

| Gates/chip                                                | 300k       | 500k       | 2M          | 5M          | 10M         | 20M          |

| Bits/Chip<br>- DRAM<br>- SRAM                             | 16M<br>4M  | 64M<br>6M  | 256M<br>64M | 1G<br>256M  | 4G<br>1G    | 16G<br>4G    |

| Wafer processing cost (\$/cm2)                            | \$4.00     | \$.390     | \$3.80      | \$3.70      | \$3.60      | \$3.50       |

| Chip Size (mm2) -logic processor -DRAM                    | 250<br>132 | 400<br>200 | 600<br>220  | 800<br>500  | 1000<br>700 | 1250<br>1000 |

| Wafer Diameter (mm)                                       | 200        | 200        | 200-<br>400 | 200-<br>400 | 200-<br>400 | 200-<br>400  |

| Defect Density<br>(Defects per cm2)                       | 0.1        | 0.05       | 0.03        | 0.01        | 0.004       | 0.002        |

| No. of interconnect levels - logic                        | 3          | 4-5        | 5           | 5-6         | 6           | 6-7          |

| Maximum Power (watts per die) -high performance -portable | 10 3       | 15<br>4    | 30 4        | 40 4        | 40-120<br>4 | 40-200       |

| Power supply Voltage (V) -desktop -portable               | 5 3.3      | 3.3<br>2.2 | 2.2 2.2     | 2.2<br>1.5  | 1.5<br>1.5  | 1.5<br>1.5   |

| No. of I/O's                                              | 500        | 750        | 1500        | 2000        | 3500        | 5000         |

| Performance (MHz) -off chip -on chip                      | 60<br>120  | 100<br>200 | 175<br>350  | 250<br>500  | 350<br>700  | 500<br>1000  |

### **TECHNICAL ARTICLES**

Five areas of critical challenges that could decrease the rate or even stop the progress of scaling of Semiconductor technology were identified:

- Patterning material and processes for device structures below 0.25µm

- Electrical interconnections, both on and off chip

- Electrical test, time cost and capability

- Design, modeling, simulation capability for all elements of IC technology and products

- Software capability, availability and quality for all aspects of IC technology and production.

As we look back at the last 15 years now at the end of 2006, this roadmap has truly focused the investment and made most of the predictions come true.

## Emergence of Foundry Manufacturing Companies

As the process technology scaling became more systematic the disaggregating of IC manufacturing became a reality. Since the establishment of TSMC in 1987 to satisfy customers' needs under the disintegration trend, the pure play foundry industry has grown to a multi-billion business. In turn, the pure play foundry business model has further accelerated the disintegration trend in the semiconductor industry.

In the past decade, leading foundry companies have caught up with the leading IDMs (Integrated Device Manufacturers) in process technology prowess. The technological challenges of foundry companies in the next decade will be even more challenging than those of leading IDMs because of the need to emphasize more on process versatility, cost effectiveness and easy adoption by diversified customers.

The specific technology development challenges of a successful foundry company in the next decade include: (1) aggressive scaling of transistors, interconnect, and design rules for both performance and density; (2) embedded technologies for SOC solutions; (3) cost effective and manufacturability process technology; (4) a versatile technology portfolio; and (5) easy integration among customers, design service/IP providers and the foundries.

In the next decade, the foundry paradigm is expected to play an even more important role as foundry companies continue to build their core competencies, including leading-edge process technologies, advanced and flexible manufacturing capabilities, and customer-oriented services systems. The strong entrenchment of the foundry industry will further move the semiconductor industry in the direction of complete disintegration.

#### Scaling continues to be the Treadmill of the Semiconductor Industry

Looking back at the last few years since the first SIA workshop, the ability to marshal and focus the invest-

16

ments of the entire industry on the key technology issues has indeed been an enabler for scaling down to 90nm. The top three among these are:

1. Sub-wavelength optical lithography (including OPC/Resolution Enhancement Techniques):

Advances in scanners and resist technology enabled printing features less than one-half of the light wavelengths. Chemically amplified resists, light polarization, phase shifting techniques (alternating apertures and attenuated), as well as comprehensive Model Based Optical Proximity Corrections of critical layer layouts, are the key enablers.

2. Extending bulk CMOS by several performance boosters - stress/strain, ultra shallow junctions, and ox nitrides:

Conventional bulk CMOS device architectures have been extended to 90 nm and below technology nodes by employing several performance boosters such as:

- bi-directional stress/strain layers to enhance carrier mobility for both electrons and holes

- ultra-shallow junctions obtained by very low energy implants and flash/laser anneal

- very thin (1.2 nm) gate ox nitride layers that provide uniform layers, good interface to both substrate and polysilicon gate and prevent Boron penetration.

- 3. Multilevel Cu interconnect including CMP:

Up to 12 layer of Cu interconnect layers have been achieved thanks to Double Damascene Cu deposition/patterning technology and improvement in chemical mechanical polishing. Dishing/erosion effects have been reduced by applying smart dummy fill and additional manufacturability layout design rules to eliminate wide lines/small spacing patterns and drastic density variations within each interconnect layer.

As we look forward to the continuation of these 30 years of scaling progress, there are similar challenges to overcome to scale to 45nm and below:

1. Device/process variability9:

Process variability sources can be categorized based on the spatial hierarchy: lot-to-lot, wafer-to-wafer, within-wafer or within-die, or root causes (random or systematic). These sources create a complicated distribution of parameters that must be addressed

by circuit designers. One of the key parameters is poly linewidth, since it has the dominant effect on MOS transistor electrical performance. For 90nm technologies, more than 50% of the variance in poly line width comes from within-die (within field) variations. The next component is die-to-die. The percentage of systematic variations increases with device scaling. For 90nm NMOS transistors, it reaches 40% of the overall Across Chip Variance (ACV).

Transistors behave differently based upon the neighborhood layout pattern due to printability and stress/strain effects. Moreover, printability and Chemical Mechanical Polishing (CMP) cause significant variations in interconnect parameters such as resistance and capacitance.

2. New device architecture (UTB, dual gates) less dependent on channel doping fluctuations:

Despite quite a few novel device architectures proposed in recent years (FinFET, Ultra Thin Body Transistor, Inverted T FET), the bulk CMOS device architecture is used virtually exclusively at 45 nm. It will most likely dominate the 32 nm nodes, although SOI substrates are gaining more acceptance. This leaves the device performance variations very susceptible to random dopant fluctuations. Performance boosters are additive and help, but also create additional variability sources which forces circuit designers to accept much higher variability and as well as leakage currents.

3. Material improvements: high-k for gate dielectrics, porous low-k for interconnects:

Several candidates for high-k materials have been explored; but although Hf or Zr based oxides/silicates provide attractive dielectric constant values and are stable, they do require interfacial SiO<sub>2</sub> layers between high-k layers and substrate/polysilicon. The final stack is not as beneficial anymore. Hence, high-k gate dielectrics are not employed in the vast majority of 45 nm technologies and only in combination with metal gates do they have a chance at 32 nm.

4. Advanced process control (especially feed forward):

Given the increasing complexity and small process windows, yield variability is a very significant problem. Baseline process variability keeps on increasing (tails of wafer yield distributions) and the present metrology/inspection static sampling plans fail at detecting excursions in-line. New approaches for yield relevant SOC and APC are needed to take advantage of the increased process observables

due to in-situ equipment sensor/FDC deployment.

5. Compact device models:

Below 100 nm, compact device models must accommodate microscopic (i.e., "non-bulk") physical effects with minimal impact on overall computational complexities. BSIM has filled this role for many technology generations as the workhorse, both for model characterization and node-to-node technology predictions. It continues to have the confidence of industry and seems likely to remain in service (with the possible exception of RF) down to about 45 nm.

More recent MOS models are formulated as functions of surface potential, rather than threshold voltage, in the channel and s/d edges. Surface potential is directly linked to intrinsic channel charge dynamics and enables addition of important physical effects with an economy of model complexity. The formulation admits an expression for transistor drive current that is continuous from accumulation to saturation, thereby avoiding the necessity of matching multiple regions.

Compact models at 65 nm have high priority needs for improvement:

- (a) scalability of sub-threshold currents and output resistance from short-to-long channel lengths, due largely to lateral doping non-uniformities

- (b) dependence of noise on voltage and geometry; i.e., considering 1/f noise dependence on random noise trap occurrences

- (c) capabilities for handling geometrical statistical fluctuations which affect noise, threshold voltage and drive current.

The above problems become more severe at 45 nm, along with the following additional priorities:

- (1) gate current scaling and dependences on novel (e.g., multi-layer) gate stacks,

- (2) carrier mobility in the channel due to layout-induced stress/strain,

- (3) statistical variations stemming from random dopant placements,

- (4) ballistic transport of carriers in intrinsic channel and

- (5) quantum mechanical effects due to confinement in thin films.

#### Summary

Scaling theory has been the organizing principle of the progress of the semiconductor industry throughout three decades. It has created a framework for continued improvement in density and cost performance and facilitated the desegregation of the entire industry

17

around design and manufacturing. Few concepts in our time have had as much influence on the economy.

#### **Acknowledgement**

I would like to thank Ping Yang, Bob Doering, Andrzej Strojwas, Robert Dutton, Bill George, Lawrence Arledge, and Alberto Sangiovanni-Vincentelli for providing perspectives on the various aspects of impact of scaling on the semiconductor industry for this paper.

#### References

- [1] R.H. Dennard, F.H. Gaensslen, V.L. Rideout, E. Bassous, and A.R. LeBlanc, "Design of Ion-Implanted MOSFET's with Very Small Physical Dimensions," *IEEE Journal of Solid-State Circuits*, Oct. 1974.

- [2] Cheney, D.W. and Grimes, W.W. Japanese Technology Policy: What's the secret (February 1991), Council on Competitiveness, pp. 1-26.

- [3] P. K. Chatterjee, W. R. Hunter, T. C. Holloway, and Y. T. Lin, "Technology Induced Non-Constant Field Scaling and its Impact on Submicron Device Performance," Dev. Res. Conf., Cornell, June 1980

- [4] Alberto Sangiovanni-Vincentelli, *Editorial*, Special Issue on CAD of VLSI, IEEE Transactions of Circuits and Systems, July 1981. and Richard Newton, Donald O. Pederson, Alberto Sangiovanni-Vincentelli, and Carlo Sequin, *Design Aids for VLSI: The Berkeley Perspective*, IEEE Transactions on Circuits and Systems, Vol. CAS-28, No. 7, pp. 660-680, July 1981

- [5] D. A. Antoniadis and R. W. Dutton, Models for Computer Simulation of Complete IC Fabrication Process. IEEE J. Solid-State Circuits, SC-14(2):412-430, and Robert Dutton: Father of TCADhttp://www10.edacafe.com/nbc/articles/view\_ar ticle.php?articleid=315936

- [6] W. Maly, A.J. Strojwas and S. W. Director, "VLSI Yield Prediction and Estimation - A Unified Framework," IEEE Trans. on CAD of ICAS, Special Issue on Statistical Design, Jan.1986

- [7] R.R. Doering and D.W. Reed, "Exploring the Limits of Cycle Time for VLSI Processing," Technical Digest of the 1994 Symposium on VLSI Technology, pp. 31-32, Honolulu, Hawaii, June 7, 1994.

- [8] Semiconductor Technology Workshop Conclusions Report 1992. Linda Wilson, International Technology Roadmaps for Semiconductors Sematech and http://www.reedelectronics.com/semiconductor/article/CA490081

- [9] A. J. Strojwas, "Conquering Process Variability: A Key Enabler for Profitable Manufacturing in Advanced technology Nodes", Keynote Paper, ISSM 2006, Tokyo, Japan, September 2006

#### **About the Author**

Dr. Pallab Chatterjee is Executive Vice President, Solutions Officer and Chief Delivery Officer of i2 Technologies, Inc.

He is responsible for Solutions Operations, which includes Solution business units for SRM and MDM, Research and Development,

Information Technology, Global Solution Center, Global Customer Solution Management and i2's India Operations.

During his tenure at i2 Dr. Chatterjee has overseen the evolution of i2's industry-leading solutions, including the development and delivery of the i2 Agile Business Process Platform and the company's new-generation supply chain management solutions. His extensive global management experience and an in-depth understanding of i2's market-leading supply chain solutions from a customer's perspective have made him a valuable addition to the i2 team since his arrival in January 2000.

Chatterjee worked at Texas Instruments from 1976-2000. During his tenure there he held various executive positions. Under his leadership as senior vice president of Research and Development and chief technology officer, the Texas Instruments Technology Labs became known as a standard for excellence acknowledged by both academia and industry. As TI's senior vice president and chairman of the Manufacturing Excellence team, he was responsible for manufacturing improvements which delivered hundreds of millions of dollars in bottom-line improvement. As president of TI's Personal Productivity Products (calculators and PC business), he contributed to increasing Texas Instruments' market share and managed more than \$1.5 billion worldwide. In the role of chief information officer, he led the global i2 and SAP implementation and process transformation for Texas Instruments.

During Chatterjee's tenure at Texas Instruments, he was a TI senior fellow in 1985, an IEEE fellow in 1986, and received the IEEE J. J. Ebers award in 1986. He was elected a member of the National Academy of Engineers in 1997.

Chatterjee has been awarded numerous patents and has written several publications on the high technology industry. He earned a Bachelor of Technology degree in electronics and communication engineering from the Indian Institute of Technology, Kharagpur, India. As a student there, he was awarded the President of India Gold Medal as the class valedictorian and the B.C. Roy Memorial Gold Medal for extracurricular excellence. He received his master's and doctorate degrees in electrical engineering from the University of Illinois, and was awarded a honorary Doctor of Science Degree from Indian Institute of Technology, Kharagpur, India.

### **Recollections on MOSFET Scaling**

By Dale L. Critchlow, IBM Fellow, Retired; Dale.Critchlow@uvm.edu

#### The Beginnings

By 1970 the MOSFET technology was finding its way into manufacturing in a number of companies. Bob Dennard and I were part of the team that developed the NMOS technology (2) in the T. J. Watson IBM Research Laboratories in the 1960s. The first IBM NMOS MOSFET product, which was entering large scale manufacturing, was a high-speed main-memory with a 50ns typical access time (100ns spec) at the board level. It used 1Kb chips (soon replaced with 2Kb chips) with a six-device cell using off-chip bipolar sense amplifiers and high level decoders proposed by Peter Pleshko and Lewis Terman (3). These chips replaced the bipolar mainmemory technology which had been introduced a couple of years earlier to replace ferrite core memory.

In mid-1970, IBM Research management was searching for a technology to fill the "file gap" between moveable head magnetic disks and random access main-memory for transaction based systems. This performance gap was being filled by expensive fixed head HDDs which had much smaller latency time than the moveable head HDDs. Don Rosenheim (Manager of Applied Research) and Sol Triebwasser challenged my department to develop a proposal for a "monolithic file" with a cost/bit of about 1 millicent/bit or 1/1000 of the projected mainmemory cost. Bob Dennard was manager of a small group including Fritz Gaensslen and Larry Kuhn which reported to me. There were a number of options including shift registers and CCDs, but Dennard as the inventor was keen on pursing the one-transistor DRAM cell. Bob did some preliminary analyses, and concluded that we would need feature sizes of about 1µm, a 5X shrink from those in manufacturing, to achieve our goals.

We realized that we would have to scale the vertical dimensions (oxide thickness and junction depth) and adjust the doping level of the substrate to maintain usable device characteristics. Further, we would have to scale the operating voltages as well to preserve reliability and limit power dissipation. In fact, we had done this twice before in the 1960s, first from 24V to 12V and then to 6V using rudimentary scaling to guide our designs. (Engineers of that era, before the advent of computer simulation, were well versed in design by similitude or scaling.) We observed that our current transistors with channel lengths of 5µm and gate oxide thickness of 100nm could be operated at 20V. Therefore, we could scale to a 4V power supply with a 1um, 20nm transistor. We noted that the circuits would consume less power and be faster. Within a few days Bob, Fritz and Larry had formalized the constant-field scaling theory and its limitations.

The implications of scaling were remarkable. If all dimensions, voltages (including threshold voltage) and

doping levels were scaled by a constant factor  $\kappa$ : a) the circuit delay was decreased by  $\kappa$ , b) the power/circuit was decreased by  $\kappa^2$ , and c) the power delay product was reduced by  $\kappa^2$ . Further, the power/unit area of silicon remained constant! These were exactly the results we needed to develop a competitive low cost memory. On the down side, there were questions about the scalability of the threshold voltage and the fact that the IR drops and RC time constants of the interconnects become more severe with scaling. Of course, there were a host of transistor design, process and reliability challenges.

At that point, we were convinced that MOSFET memory would replace fixed head files. Further, we speculated that it may also replace moveable head disk storage for some applications. We also started to believe that the MOSFET would someday replace the bipolar transistor in high-performance logic and memory applications.

## Driving the Demonstration and Implementation of Scaling was Key

Bob Dennard's most profound contributions were to demonstrating the feasibility of MOSFET scaling, and then leading the way into implementation in real products. He worked with a succession of very talented engineers over several decades, providing guidance as well as continuing to make significant technical contributions.

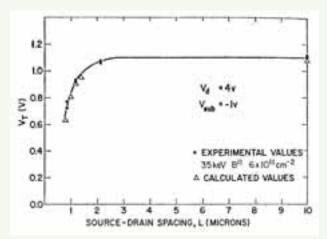

The principles of scaling were first presented at the 1972 IEDM (4) along with the design and experimental characteristics of an ion-implanted 1µm transistor with a 20nm gate oxide<sup>2</sup> which had been optimized for scaling. One of the original slides used to describe scaling is shown in Fig. 1. (Bob remembers a high degree of skepticism about the feasibility of 20nm

Fig. 1 Slide from 1972 IEDM showing some of the scaling principles.

19