#### Rückwärtsbetrieb

Im Rückwärtsbetrieb (Bild 1.10, III. Quadrant) ist der kollektorseitige pn-Übergang des IGBT in Sperrichtung gepolt und unterbindet die beim MOSFET vorhandene Inversleitfähigkeit.

Obwohl - bedingt durch die breite n'-Driftzone - zumindest bei NPT-IGBTs strukturell hier eine hochsperrende pin-Diode vorliegt, beträgt die Rückwärtssperrspannung heutiger IGBTs nur einige 10 V. Die Ursache hierfür liegt im einseitig auf hohe Vorwärtssperrspannung und gute kollektorseitige Wärmeabführung ausgerichteten Chipdesign, sowie der Ausführung der Randbereiche.

IGBT-Schalter, die für Einsatzfälle mit Rückwärtsbeanspruchung vorgesehen sind, werden deshalb bisher ausschließlich mit angepaßten, schnellen Reihendioden in hybrider Bauform versehen.

Die Durchlaßeigenschaften von IGBT-Modulen im stationären Rückwärtsbetrieb resultieren damit ausschließlich aus den Eigenschaften der externen oder hybriden Beschaltungsdioden, vgl. Kap. 1.3.

# 1.2.3 Qualitatives Schaltverhalten von MOSFET und IGBT beim harten Schalten

Der überwiegende Anteil der Schaltaufgaben für Transistorschalter erfordert "hartes" Ein- und Ausschalten ohmsch-induktiver Lasten mit nichtlückendem Laststrom, d.h. die Lastzeitkonstante L/R ist viel größer als die Periodendauer 1/f der Schaltfrequenz.

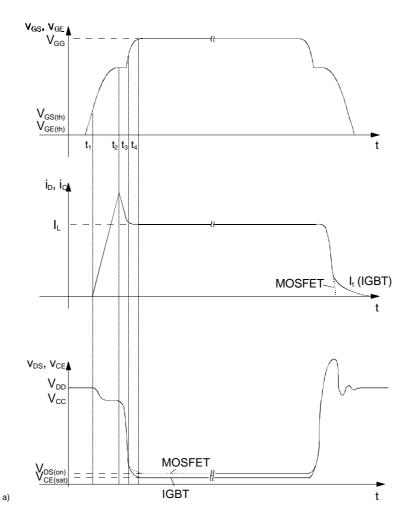

Die hieraus resultierenden, grundsätzlichen Verläufe von Drain- bzw. Kollektorstrom und Drain- Source- bzw. Kollektor-Emitter-Spannung zeigt Bild 1.11a.

29

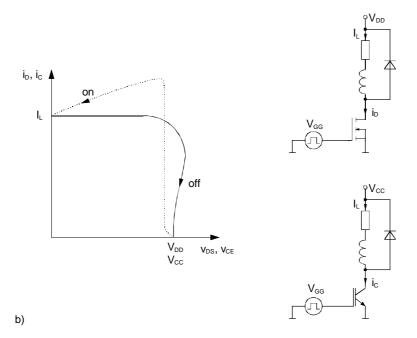

Bild 1.11 Typisches Schaltverhalten von Leistungs-MOSFET und IGBT beim "harten Schalten" (ohmschinduktive Last mit Freilaufkreis)

- a) Strom- und Spannungsverläufe

- b) Arbeitspunktverläufe und Meßschaltung

Wie bereits in Kap. 0 anhand Bild 0.4 dargestellt, ist charakteristisch für "hartes Schalten", daß während des Ein- und Ausschaltens kurzzeitig sowohl Transistorstrom als auch Transistorspannung hoch sind.

Im Gegensatz zu allen Thyristoren sind Transistoren dieser Betriebsweise prinzipiell auch ohne Beschaltung mit passiven Kommutierungsnetzwerken gewachsen, da während des Schaltens in der Driftzone eine "dynamische" Sperrschicht aufgebaut werden kann.

Im Transistor werden jedoch beträchtliche Schaltverlustenergien

$$\mathbf{E}_{\text{on}}, \mathbf{E}_{\text{off}} = \int_{t_{\text{on}}, t_{\text{off}}} \mathbf{u} \cdot \mathbf{i} dt$$

umgesetzt, wie auch die Darstellung der Arbeitspunktverläufe während des Schaltens in Form eines Graphen  $i_c = f(v_{CE})$  (bzw.  $i_D = f(v_{DS})$ ) in Bild 1.11b verdeutlicht.

Durch Beschaltung mit passiven (Schaltentlastungs-) Netzwerken kann der Arbeitspunktverlauf dichter an die Achsen angeschmiegt werden. Schaltverluste werden aus dem Transistor in die Beschaltung "verlagert", der Gesamtwirkungsgrad sinkt zumeist ab (Kap. 3.8).

Da - neben Strom-/Spannungseckwerten und Schaltzeit - noch andere (nichtideale) Effekte in den Transistoren die Form des "weitestmöglichen" Arbeitspunktverlaufes bestimmen, wird dieser für unterschiedliche Betriebsfälle in den Datenblättern als SOA (Safe Operating Area) angegeben, vgl. Kap. 2.1.2, 2.2.3 und 2.3.3.

Außer den nachfolgend behandelten, nichtidealen Eigenschaften der Transistoren und den in Kap. 1.3 beschriebenen Diodeneigenschaften beeinflussen auch passive Stromkreiselemente die Schaltverluste und Arbeitspunktverläufe in hohem Maße. Deren Auswirkungen, die in Bild 1.11a und b ebenfalls angedeutet sind, werden in Kap. 3.4.1 noch näher beschrieben.

Physikalische Ursache der typischen Strom-Spannungsverläufe in Bild 1.11a ist die Wirkung der Freilaufdiode, die ein Abreißen des Stromes durch die Lastinduktivität verhindern muß:

- Beim Einschalten des Transistors kann die Freilaufdiode erst Sperrspannung aufnehmen (ausschalten), wenn der volle Laststrom auf den Transistor kommutiert ist. Der Kollektorbzw. Drainstrom muß deshalb die Höhe des Laststromes erreichen, bevor die Kollektor-Emitter- (bzw. Drain-Source-) Spannung auf den Durchlaßwert absinken kann.

- Beim Ausschalten des Transistors kann die Freilaufdiode den Laststrom erst dann übernehmen (einschalten), wenn sie in Durchlaßrichtung gepolt ist. Hierzu muß die Kollektor-Emitter- (bzw. Drain-Source-) Spannung über das Niveau der Kommutierungsspannung angestiegen sein, bevor der Kollektor- bzw. Drainstrom auf den Wert des Reststromes sinken kann.

Wie Bild 1.11a qualitativ zeigt, sinken beim *Einschalten* des MOSFET oder IGBT die Drain-Source- bzw. Kollektor-Emitter-Spannung vergleichbarer Bauelemente zunächst im gleichen Maße innerhalb einiger zehn Nanosekunden bis auf einen Wert ab, der dem Spannungsabfall über dem n-Bahngebiet entspricht. Während dies beim MOSFET bereits die Durchlaßspannung  $V_{DS(on)} = I_D \cdot R_{DS(on)}$  repräsentiert, setzt beim IGBT nunmehr die Überflutung des n-Gebietes mit positiven Ladungsträgern aus der p-Kollektorzone ein. Nach Abschluß dieses Vorganges (ca. 100 ns bis einige  $\mu$ s) ist die - bei hochsperrenden Elementen - vergleichsweise niedrigere Durchlaßspannung  $V_{CE(sat)}$  als statischer Endwert erreicht (Leitwertmodulation).

Beim *Ausschalten* müssen beim MOSFET lediglich die internen Kapazitäten soweit umgeladen werden, daß die Ladungsträgerinfluenz im Kanalgebiet unterbleibt. Nachfolgend kommt es zu einem sehr schnellen Abbau der Neutralitätsstörung in diesem Bereich, und der Drainstrom sinkt steil ab.

Im IGBT findet zunächst der gleiche Vorgang statt. Nach dem Erlöschen des Emitterstromes sind im n $\bar{}$ -Bahngebiet jedoch noch ein großer Teil der durch die Injektion aus dem IGBT-Kollektorgebiet erzeugten p-Ladungsträger vorhanden. Diese müssen nun rekombinieren oder durch Rückinjektion abgebaut werden, was einen sogenannten Kollektorstromschweif (Tailstrom  $I_t$ ) hervorruft (Bild 1.11a).

Da dieser Stromschweif innerhalb von µs erst bei bereits angestiegener Kollektor-Emitter-Spannung abklingt, werden beim harten Schalten die IGBT-Ausschaltverluste wesentlich durch den Schweifstromverlauf bestimmt (vgl. Kap. 2.3.2, 3.1.3) und übersteigen die vergleichbarer MOSFETs beträchtlich.

Abgesehen von den erläuterten Unterschieden ähnelt sich das Schaltverhalten von MOSFETs und IGBTs aufgrund des gleichartigen Gatezonenaufbaues weitgehend.

Wie im Kap. 1.2.1 beschrieben, beeinflussen die *internen Bipolartransistorstrukturen* und *internen, lateralen Widerstände* das Durchlaß- und Vorwärtssperrvermögen, die Eigenschaften in Rückwärtsrichtung sowie die Grenzen der transienten Strom- und Spannungsbelastbarkeit beim Schalten.

Das Schaltverhalten (Schaltgeschwindigkeit, Schaltverluste) der MOSFET- und IGBT-Leistungsmodule wird durch deren strukturbedingte, *interne Kapazitäten (Ladungen)* und die *internen und Anschlußwiderstände* bestimmt.

Entgegen der Idealvorstellung einer leistungslosen Spannungssteuerung über das MOSFETbzw. IGBT-Gate resultiert aus den beim Schalten notwendigen *Umladeströmen* der internen Kapazitäten ein schaltfrequenzabhängiger *Bedarf an Ansteuerleistung*, vgl. Kap. 3.5.

Weiterhin beeinflussen die bei der Zusammenschaltung von Transistorchips in Leistungsmodulen entstehenden und in deren Zuleitungen vorhandenen parasitären Verbindungsinduktivitäten

die Kommutierungsvorgänge, induzieren transiente Überspannungen und können mit den stromkreis- und transistorinternen Kapazitäten Schwingungen anregen, vgl. Kap. 3.4.

Im folgenden soll das Schaltverhalten von MOSFET und IGBT in Abhängigkeit von den transistorinternen Kapazitäten und Widerständen analysiert werden.

Bei ausgeschaltetem MOSFET (IGBT) ist  $C_{GD}$  ( $C_{GC}$ ) klein und entspricht etwa  $C_{DS}$  ( $C_{CE}$ ).

Im Durchlaßzustand wächst  $C_{GD}$  ( $C_{GC}$ ) infolge Inversion der Anreicherungsschicht unter den Gatezonen sprunghaft an, sobald die Gate-Source(Emitter)-Spannung größer als die Drain-Source(Kollektor-Emitter)-Spannung wird.

Während des Schaltens wird  $C_{GD}$  ( $G_{GC}$ ) zusätzlich aufgrund des Miller-Effektes dynamisch vergrößert:

$$\begin{split} &C_{GDdyn} = C_{GD} \; ( \; 1\text{-}\; dv_{DS}/dv_{GS}) \; \; (MOSFET) \\ &C_{GC\; dyn} = C_{GE} \; ( \; 1\text{-}\; dv_{CE}/dv_{GE}) \; \; (IGBT) \end{split}$$

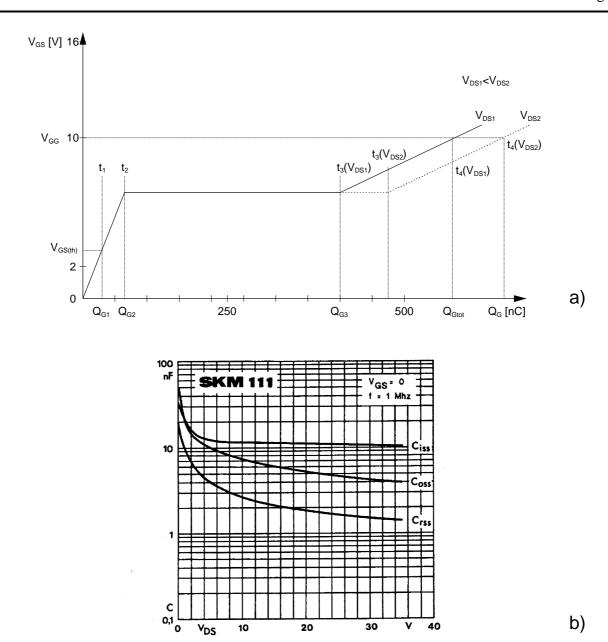

In den Datenblättern sind meist die folgenden Kleinsignal-Kapazitäten des ausgeschalteten Transistors mit ihrer Spannungsabhängigkeit dargestellt, vgl. Kap. 2.2.2, 2.2.3.

| Leistungs-MOSFET            | IGBT                        |                       |

|-----------------------------|-----------------------------|-----------------------|

| $C_{iss} = C_{GS} + C_{GD}$ | $C_{iss} = C_{GE} + C_{GC}$ | Eingangskapazität     |

| $C_{rss} = C_{GD}$          | $C_{rss} = C_{GC}$          | Rückwirkungskapazität |

| $C_{oss} = C_{GD} + C_{DS}$ | $C_{oss} = C_{GC} + C_{CE}$ | Ausgangskapazität     |

Zur Berechnung des Schaltverhaltens sind diese Angaben nur sehr eingeschränkt nutzbar, da z.B.  $C_{iss}$  und  $C_{rss}$  im durchgesteuerten Transistor ( $V_{DS} < V_{GS}$  bzw.  $V_{CE} < V_{GE}$ ) nochmals stark ansteigen, was in den meisten Datenblättern nicht erfaßt ist (Bild 1.12 und Bild 1.13) [277].

Als Hilfsmittel für die Bestimmung der Schaltzeiten in Abhängigkeit von Gatestrom, Drain-Source-Spannung und Drainstrom wird deshalb in den Datenblättern das "Gateladungsdiagramm" des MOSFET angegeben, in dem für den "Nennstrom" und 20 % bzw. 80 % der höchstzulässigen Drain-Source-Spannung der Verlauf der Gate-Source-Spannung über der dem Gate zugeführten Ladungsmenge Q<sub>G</sub> aufgetragen ist (Bild 1.12).

Lastbedingungen und Meßschaltung entsprechen Bild 1.11. Vereinfachend wird jedoch Konstantstromeinspeisung in das Gate angenommen.

Über die Beziehung

$$i_G = dQ_G/dt$$

können dann recht einfach die Schaltzeitintervalle bestimmt werden, vgl. Kap. 3.5.1.

Bild 1.12 a) Verlauf der Gate-Source-Spannung  $V_{GS}$  eines Leistungs-MOSFET-Modules in Abhängigkeit von der Gateladung  $Q_G$  (Gateladungsdiagramm)

b) Kleinsignal-Kapazitäten eines Leistungs-MOSFET

# Einschalten: Schaltzeitintervall 0...t1 (gesperrter Transistor)

Mit Zuschalten der Steuerspannung beginnt der Gatestrom zu fließen.

Bis zur Ladungsmenge  $Q_{G1}$  lädt  $i_G$  zunächst ausschließlich die Gatekapazität  $C_{GS}$  auf; die Gatespannung  $V_{GS}$  steigt an. Da  $V_{GS}$  noch kleiner als die Schwellenspannung  $V_{GS(th)}$  ist, kann in diesem Zeitintervall noch kein Drainstrom fließen.

## **Einschalten: Schaltzeitintervall** t<sub>1</sub>...t<sub>2</sub> (**Drainstromanstieg**)

Ist  $V_{GS}$  zum Zeitpunkt  $t_1$  bis auf  $V_{GS(th)}$  angestiegen, schaltet der Transistor ein und durchläuft dabei zunächst den *aktiven Arbeitsbereich* (s. Kap. 1.2.2.1).

Der Drainstrom steigt bis auf  $I_L$  (ideale Freilaufdiode) bzw. - wie im Bild 1.11a für eine reale Freilaufdiode angedeutet - über  $I_L$  hinaus an. In gleicher Weise wächst  $V_{GS}$ , die im aktiven Be-

reich über die Steilheit  $g_{fs}$  mit  $I_D = g_{fs} * V_{GS}$  mit dem Drainstrom verkoppelt ist, bis auf den Wert  $V_{GS1} = I_D/g_{fs}$  (Zeitpunkt  $t_2$ ).

Da die Freilaufdiode erst zu  $t_2$  sperren kann, fällt  $V_{DS}$  vor  $t_2$  nicht nennenswert ab.

Zu  $t = t_2$  ist die Ladungsmenge  $Q_{G2}$  in das Gate geflossen.

#### **Einschalten: Schaltzeitintervall t2...t3 (durchschaltender Transistor)**

Mit dem Ausschalten der Freilaufdiode sinkt  $V_{DS}$  bis zum Zeitpunkt  $t_3$  soweit ab, daß ihr Durchlaßwert  $V_{DS(on)}$  nahezu erreicht ist. Zwischen  $t_2$  und  $t_3$  sind Drainstrom und Gate-Source-Spannung weiterhin über die Steilheit verkoppelt;  $V_{GS}$  bleibt deshalb konstant. Während des Abfallens von  $V_{DS}$  lädt der Gatestrom  $i_G$  mit der Ladungsmenge ( $Q_{G3}$ - $Q_{G2}$ ) die Millerkapazität  $C_{GD}$  um. Bis  $t=t_3$  ist die Ladungsmenge  $Q_{G3}$  in das Gate geflossen.

### Einschalten: Schaltzeitintervall t<sub>3</sub>...t<sub>4</sub> (ohmscher Kennlinienbereich)

Zum Zeitpunkt  $t_3$  ist der Transistor eingeschaltet, und sein Arbeitspunkt ist vom Abschnürbereich in den ohmschen Arbeitsbereich eingetreten.  $V_{GS}$  und  $I_D$  sind nicht mehr über  $g_{fs}$  verkoppelt.

Die nunmehr dem Gate zugeführte Ladungsmenge ( $Q_{Gtot}$ - $Q_{G3}$ ) bewirkt das weitere Ansteigen von  $V_{GS}$  bis zur Höhe der Gate-Steuerspannung  $V_{GG}$ . Da der reale Einschaltwiderstand  $R_{DS(on)}$  von  $I_D$  und  $V_{GS}$  abhängig ist, kann über die insgesamt dem Gate zugeführte Ladungsmenge  $Q_{Gtot}$  die Durchlaßspannung  $V_{DS(on)} = I_D * R_{DS(on)}$  in Grenzen bis zum physikalischen Minimum eingestellt werden.

Die zum Erreichen einer bestimmten Gate-Source-Spannung notwendige Ladungsmenge  $Q_{Gtot}$  ist um so größer, je höher die Drainspannung  $V_{DD}$  (bzw. Kommutierungsspannung) ist, vgl. Bild 1.12.

#### Ausschalten

Während des Ausschaltvorganges verlaufen die beschriebenen Vorgänge in umgekehrter Richtung; die Ladung  $Q_{\text{Gtot}}$  muß mittels Steuerstrom wieder aus dem Gate abgeführt werden.

Näherungsweise kann deshalb das Gateladungsdiagramm nach Bild 1.12 auch zur quantitativen Bestimmung des Ausschaltvorganges herangezogen werden.

Je weiter der Einsatzfall des Transistormodules vom hier betrachteten Fall "Hartschalter" abweicht, um so mehr "verwischt" sich die Treppenform der Gate-Source-Spannung. Die beim harten Schalten durch das Verhalten der Freilaufdiode "entkoppelten" Intervalle gehen dann mehr oder weniger ineinander über und die genaue Beschreibung des Schaltverhaltens wird komplexer [278].

Für IGBT-Leistungsmodule treffen die dargestellten Betrachtungen sinngemäß in gleicher Weise zu. Die Bestimmung des Schaltverhaltens kann analog am ebenfalls in den Datenblättern vorhandenen Gateladungsdiagramm erfolgen.

Da das Gate eines IGBT meist zwischen einer positiven und einer negativen Steuerspannung umgeschaltet wird, wird hier auch ein Ladungsanteil zur Umladung der Gatekapazität zwischen 0 V und  $V_{GG-}$  benötigt. Zur Ermittlung der Gesamt-Gateladungen muß deshalb das Gateladungsdiagramm in der in Bild 1.13 dargestellten Weise erweitert werden.